iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

# SQ7615 Datasheet V1.3

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

#### Content

| 1. CHANGE HISTORY                      |    |

|----------------------------------------|----|

| 2.PRODUCT OVERVIEW                     |    |

| 2.1 FEATURES                           |    |

| 2.2 Preface                            |    |

| 2.3 Block Diagram                      |    |

| 2.4 PIN Assignment/Description         |    |

| 2.5 I/O CIRCUIT TYPE                   |    |

| 3. ELECTRONIC CHARACTERISTICS          |    |

| 3.1 Absolute Maximum Ratings           |    |

| 3.2 Operation Conditions               |    |

| 3.2.1 Operation Conditions             |    |

| 3.2.2 Clock Timing                     |    |

| 3.2.3 I/O Characteristics              |    |

| 3.3 D.C. Characteristics               |    |

| 3.4 Power-on Reset Characteristics     |    |

| 3.5 BROR Characteristics               |    |

| 3.6 LVD CHARACTERISTICS                |    |

| 3.7 ADC CHARACTERISTICS                |    |

| 3.8 Flash Characteristics              |    |

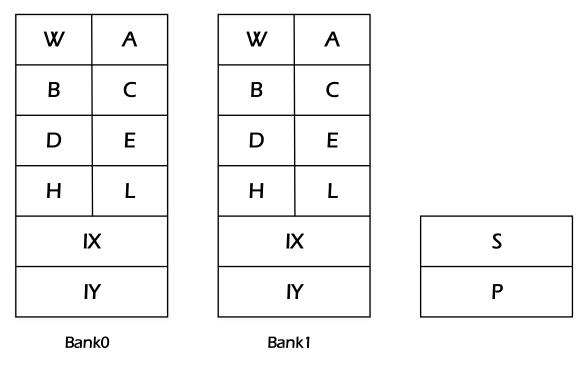

| 4. CENTRAL PROCESSING UNIT (CPU)       |    |

| 4.1 Symbols                            |    |

| 4.2 Core Register                      |    |

| 4.2.1 8-bit General Purpose Registers  |    |

| 4.2.2 16-bit General-Purpose Register  |    |

| 4.2.3 Program Status Word (PSW)        |    |

| 4.2.4 Stack Pointer (SP)               |    |

| 4.2.5 Program Counter (PC)             |    |

| 4.3 Addressing Mode                    |    |

| 4.3.1 Register Indirect Addressing     |    |

| 4.3.2 Direct Addressing                | 42 |

| 4.3.3 Register Addressing (r or rr)    |    |

| 4.3.4 Immediate Addressing (n or mn)   |    |

| 4.3.5. Relative Addressing             |    |

| 4.3.6 Absolute Addressing              |    |

| 4.3.7 Vector Addressing                |    |

| 4.3.8 Direct Bit Addressing            |    |

| 4.3.9 Register Indirect Bit Addressing |    |

| 4.4 Instruction Pipeline Stages        |    |

| 4.4.1 Register-to-Register Operations  |    |

| 4.4.2 Register-to-Memory Operations    |    |

| 4.4.3 Memory-to-Register Operations    |    |

| 4.4.4 Memory-Memory Operations         |    |

| 4.4.5 Jump                             |    |

| 4.4.6 Subroutine Call and Return       |    |

| 4.4.7 SWI                              |    |

| 4.5 Instruction Set Summary            | 50 |

# iMQ Technology Inc.

| No.: TDD  | 501-S7615-EN           | Name: SQ7615 Datasheet      | Version: V1.3 |

|-----------|------------------------|-----------------------------|---------------|

| 4.5.1     | Move/Load/Store and    | Exchange Instructions       | 50            |

| 4.5.2     |                        |                             |               |

| 4.5.3     | Shift/Rotate and Nibbl | e Manipulation Instructions | 54            |

| 4.5.4     | •                      | tion Instructions           |               |

| 4.5.5     | Jump Instructions      |                             | 57            |

| 4.5.6     | Call, Return, Software | Interrupt and No Operation  | 58            |

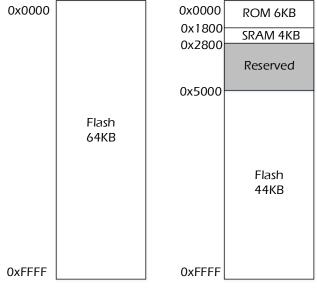

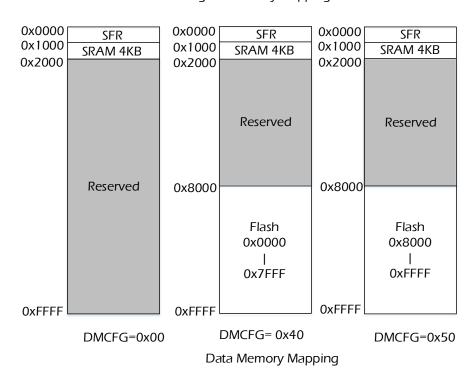

|           | ESSING SPACE           |                             | 59            |

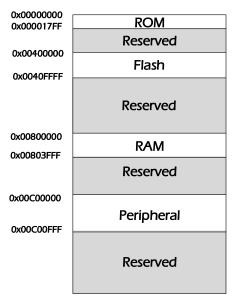

| 5.1 PLA   | TEFORM MEMORY ORGANIZ  | ZATION                      | 61            |

| 5.1.1     |                        | er                          |               |

|           |                        | d Control Registers         |               |

| 5.2 Per   | RIPHERAL MEMORY        |                             | 70            |

| 5.2.1     |                        |                             |               |

| 6. SYSTEM | OPERATION              |                             | 74            |

| 6.1 OPER  | RATING MODES           |                             | 74            |

| 6.1.1     | Normal Mode            |                             | 76            |

| 6.1.2     | Sleep Mode             |                             | 76            |

| 6.1.3     | Deep Sleep Mode        |                             | 76            |

| 6.1.4     | Low Power Mode         |                             | 77            |

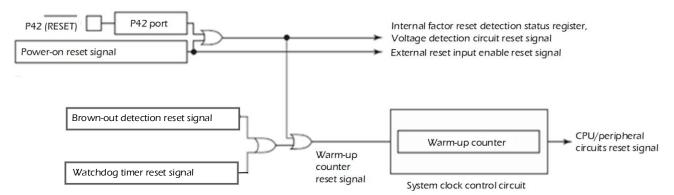

| 6.2 Rese  | T FUNCTION             |                             | 78            |

| 6.2.1     | Configuration          |                             | 78            |

| 6.2.2     | Control                |                             | 79            |

| 6.2.3     | Function               |                             | 81            |

| 6.2.4     | Device Initialization  |                             | 82            |

| 6.2.5     | Reset Signal Generatin | g Factors                   | 84            |

| 6.3 Po    |                        |                             |               |

| 6.3.1     | Configuration          |                             | 87            |

| 6.3.2     | Function               |                             | 87            |

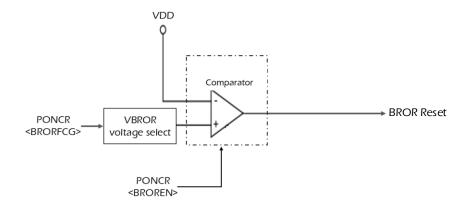

| 6.4 Bro   | OWN-OUT RESET (BROR)   |                             | 88            |

| 6.4.1     | Configuration          |                             | 88            |

| 6.4.2     | Function               |                             | 88            |

| 6.4.3     | Control                |                             | 89            |

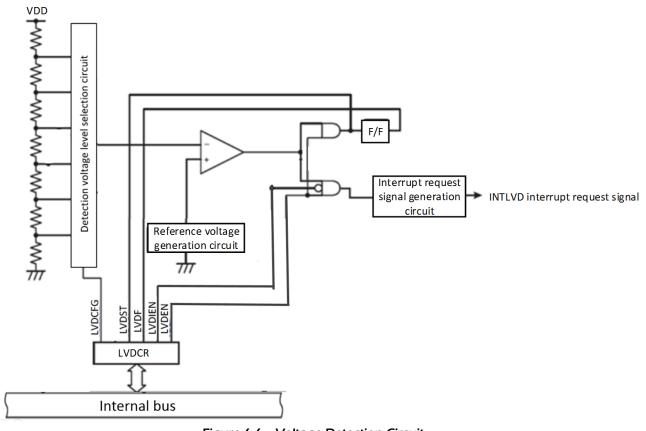

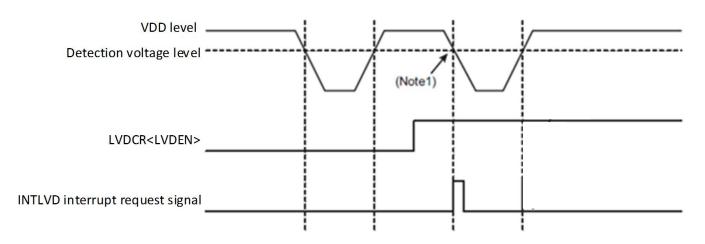

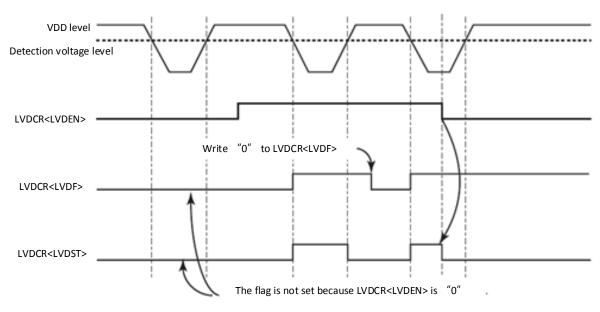

| 6.5 VOLT  | rage Detection Circuit |                             | 90            |

| 6.5.1     | Configuration          |                             | 90            |

| 6.5.2     | Control                |                             | 92            |

| 6.5.3     | Function               |                             | 93            |

| 6.5.4     | Register Setting       |                             | 95            |

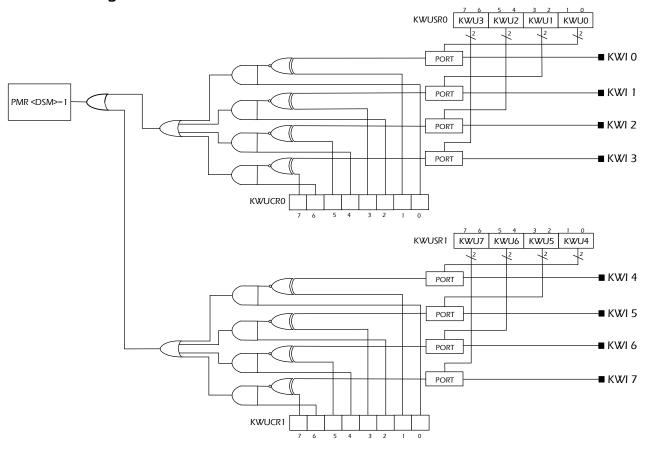

| 6.6 KEY-0 |                        |                             |               |

| 6.6.10    | Configuration          |                             | 96            |

| 6.6.2     | Control                |                             | 97            |

| 6.6.3     | Function               |                             | 100           |

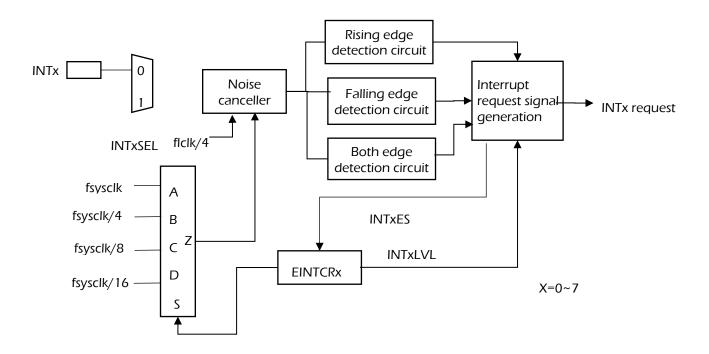

| 6.7 INT   | ERRUPT                 |                             | 101           |

| 6.7.1     | Non-Maskable Interruj  | ots                         | 101           |

| 6.7.2     | Maskable Interrupts    |                             | 101           |

| 6.7.3     |                        |                             |               |

| 6.7.4     | Nested Vectore Interru | Dt Controller (INTC)        | 105           |

| 6.7.5     |                        | (IFRx , x=0~11)             |               |

| 6.7.6     |                        | ter (IERx) ,x=0~11          |               |

|           |                        |                             |               |

# iMQ Technology Inc.

| No. | : TDDS         | 501-S7615-EN               | Name: SQ7615 Datasheet | Version: V1.3 |

|-----|----------------|----------------------------|------------------------|---------------|

|     | 6.7.7          | Interrupt Processina       |                        | 109           |

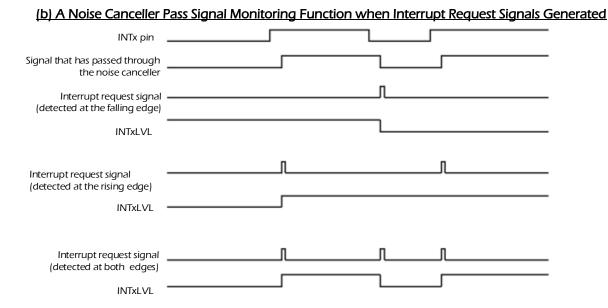

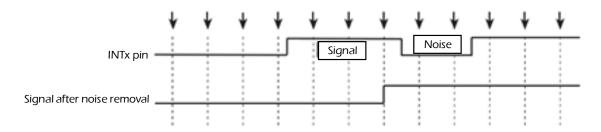

| 6.  |                |                            | CIRCUIT                |               |

|     | 6.8.1          | Configuration              |                        | 110           |

|     | 6.8.2          |                            |                        |               |

|     | 6.8.3          | External Interrupt functio | n                      | 112           |

| 6.  | 9 Sys          | TEM POWER MONITOR          |                        | 117           |

|     | 6.9.1          | System Power Monitor Con   | itrol Registers        | 117           |

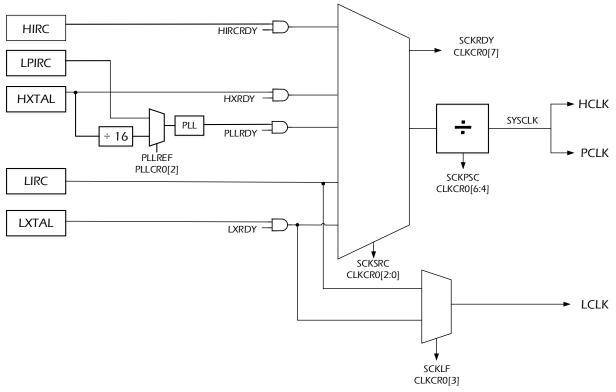

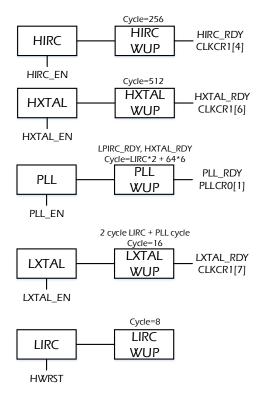

| 7.  | <b>SYSTEI</b>  | M CLOCK CONTROLLER         | -                      | 119           |

| 7.  | .1 <b>C</b> LC | OCK SOURCE                 |                        | 119           |

|     |                |                            |                        |               |

|     |                |                            |                        |               |

| 7.  |                |                            |                        |               |

| 7.  |                |                            |                        |               |

| _   | 7.5.1          |                            |                        |               |

| 8.  |                |                            |                        |               |

| 8.  |                |                            |                        |               |

|     | 8.1.1          |                            |                        |               |

|     | 8.1.2          |                            | _                      |               |

|     | 8.1.3          |                            | g                      |               |

|     | 8.1.4          |                            |                        |               |

|     | 8.1.5<br>8.1.6 |                            |                        |               |

|     | 8.1.7          |                            |                        |               |

|     | 8.1.8          | •                          |                        |               |

|     | 8.1.9          | •                          |                        |               |

|     |                |                            |                        |               |

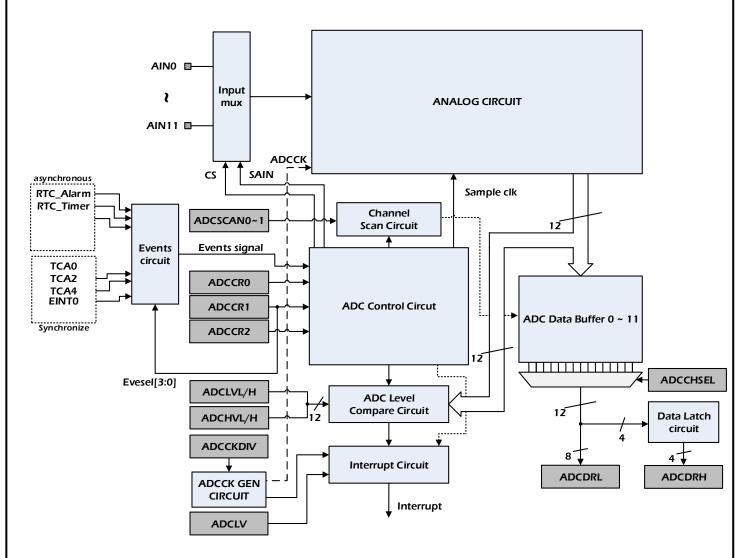

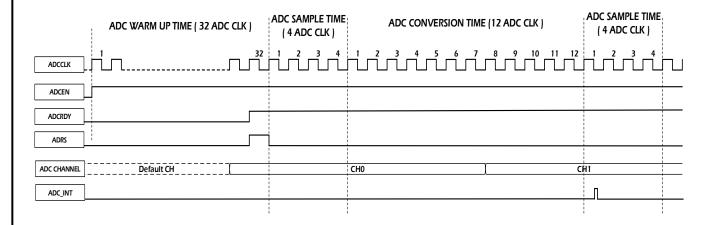

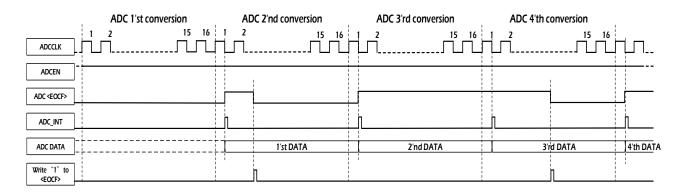

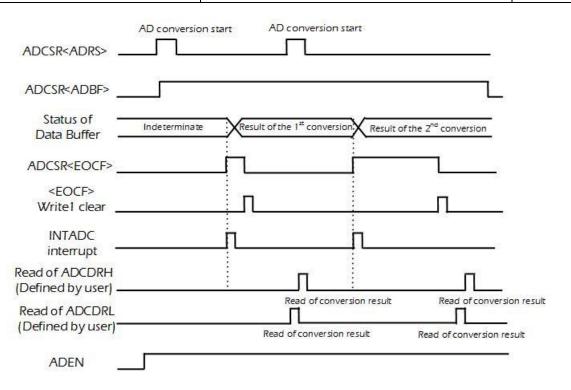

|     | 8.1.11         | ADC Register Setting       |                        | 140           |

| Q   |                |                            | IVERTER                |               |

| 0.  | 8.2.1          |                            | range                  |               |

|     | 8.2.2          |                            | s input/output ports   |               |

|     |                |                            | s ii pay satpat poi a  |               |

| 8.  |                |                            |                        |               |

|     |                |                            | FMC)                   |               |

|     |                | -                          |                        |               |

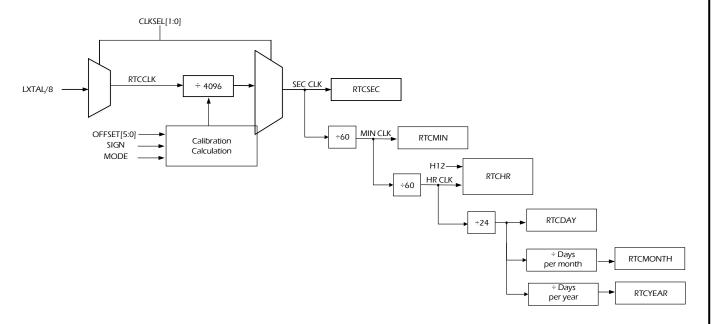

| 9.  |                |                            | R                      |               |

|     |                |                            |                        |               |

| 10  | 0.1 10 1       | PORT CONTROL REGISTER      |                        | 160           |

| 10  | 0.2 IC         | PORT REGISTER              |                        | 161           |

|     | 10.2.1         | Port P0 Register           |                        | 161           |

|     | 10.2.2         | Port P1 Register           |                        | 164           |

|     | 10.2.3         |                            |                        |               |

|     | 10.2.4         |                            |                        |               |

|     | 10.2.5         |                            |                        |               |

|     | 10.2.6         |                            |                        |               |

|     |                |                            |                        |               |

|     |                |                            |                        |               |

| 1   | 1.2 Mu         | LTIPLIER REGISTERS         |                        | 177           |

# iMQ Technology Inc.

| No. : TDDS01-S7615-EN        | Name: SQ7615 Datasheet                 | Version: V1.3 |

|------------------------------|----------------------------------------|---------------|

| 12 PHERIPHERAL NETWORK INTE  | R-CONNECT (PNIC)                       | 182           |

|                              |                                        |               |

| 12.2 OPERATION FLOWCHART     |                                        | 183           |

| 12.3 CONTROL                 |                                        | 184           |

| 12.4 PNIC DIAGRAM            |                                        | 191           |

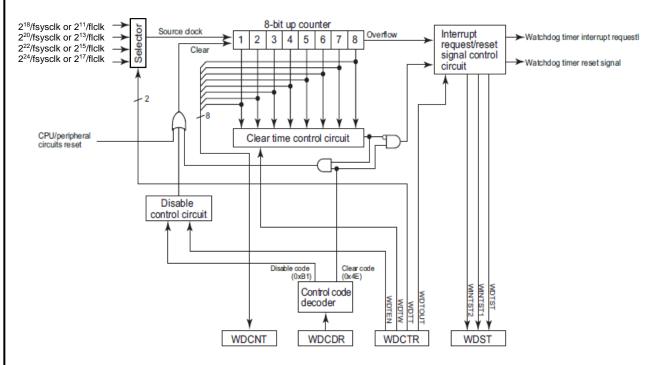

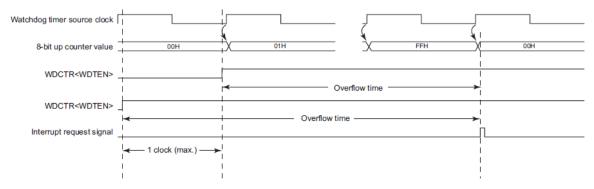

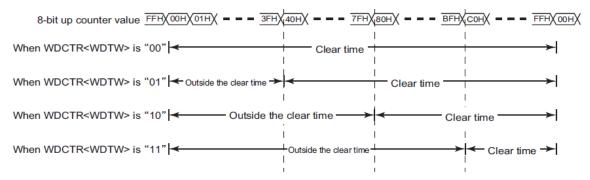

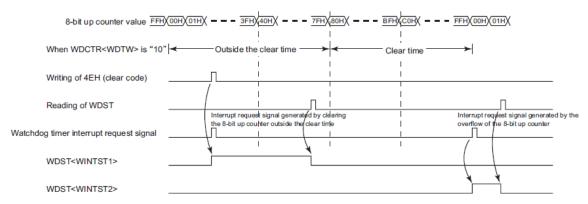

| 13. WATCHDOG TIMER (WDT)     |                                        | 192           |

| 13.1 WATCHDOG TIMER (WDT)    |                                        | 192           |

| 13.1.1 Watchdog Timer Confi  | guration                               | 192           |

| 13.1.2 Watchdog Timer Contr  | ol                                     | 193           |

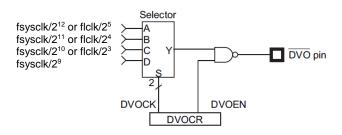

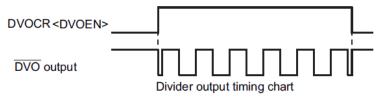

| 13.2 DIVIDER OUTPUT (DVOB)   |                                        | 201           |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

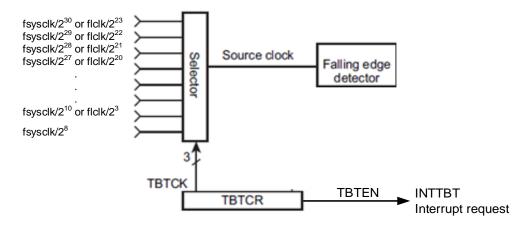

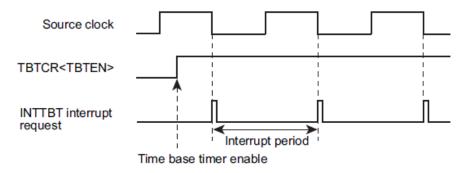

| 13.3 TIME BASE TIMER (TBT)   |                                        | 204           |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

| 13.5.2 Low Power Consumption | n Function                             | 230           |

|                              |                                        |               |

|                              |                                        |               |

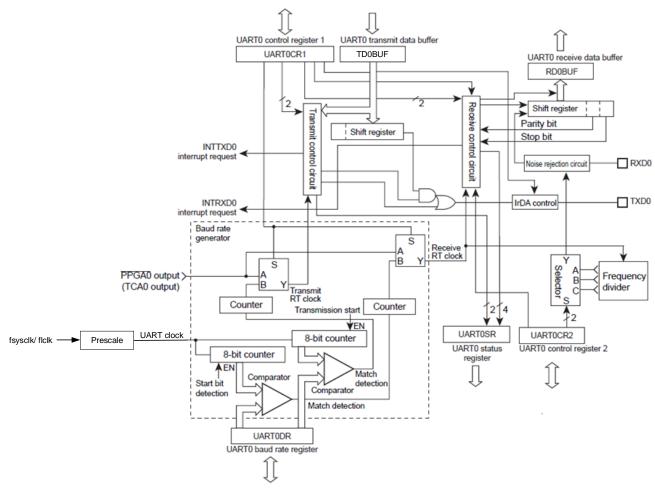

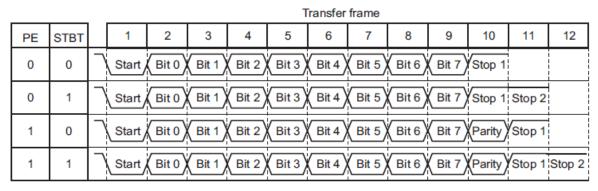

|                              | RFACE (UART)                           |               |

|                              |                                        |               |

|                              |                                        |               |

|                              | OUARTOCR2 REGISTERS FROM BEING CHANGED |               |

|                              |                                        |               |

|                              | ER MODE                                |               |

|                              | J-4' M-4I J                            |               |

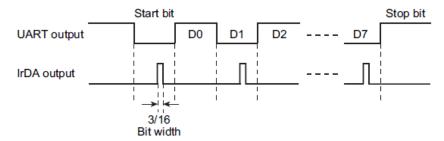

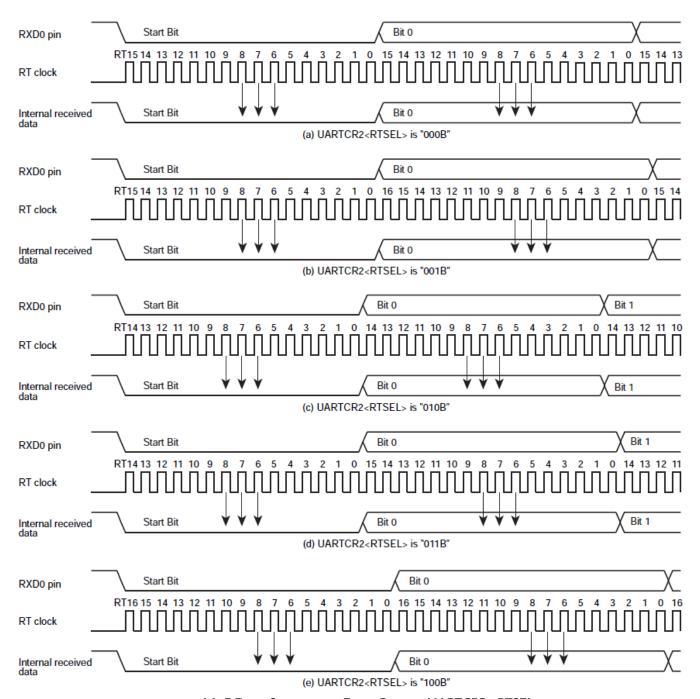

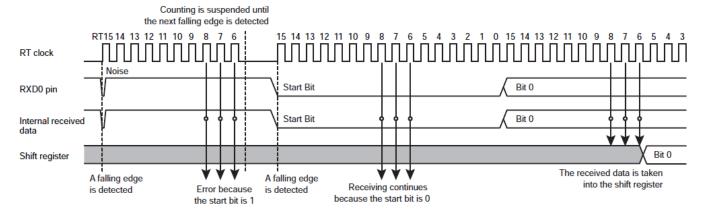

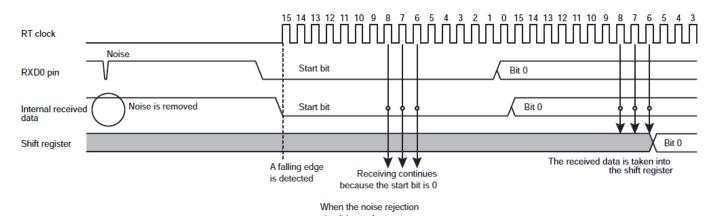

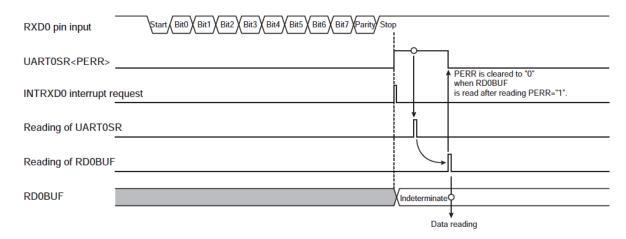

|                              | ılation Method                         |               |

|                              |                                        |               |

|                              | N                                      |               |

|                              |                                        |               |

|                              | l                                      |               |

| •                            |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

| <u> </u>                     |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

|                              |                                        |               |

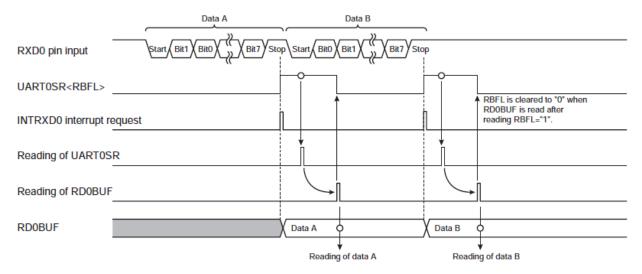

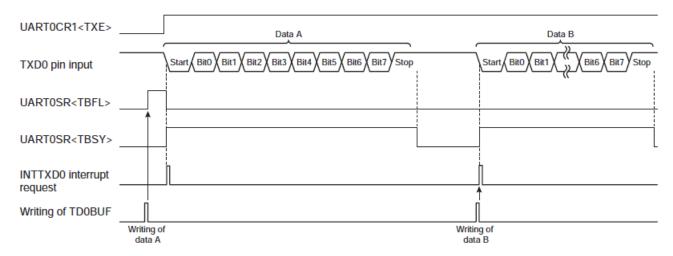

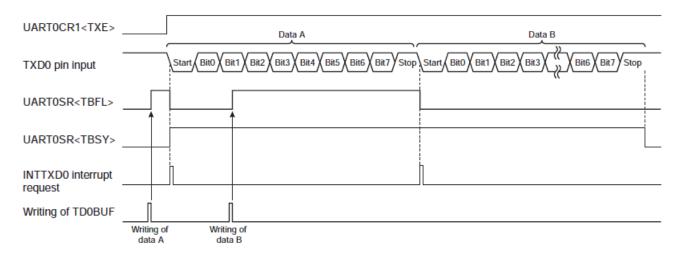

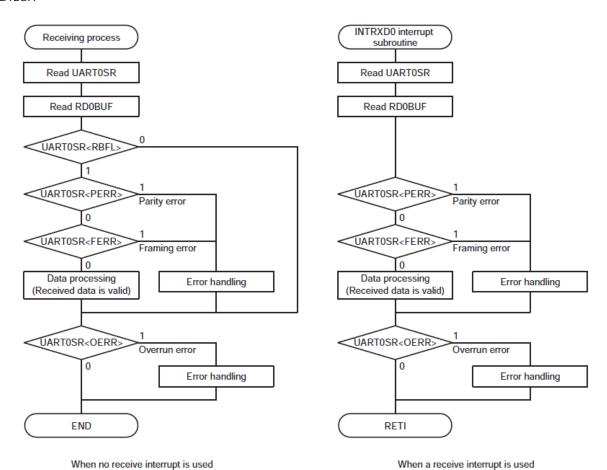

| I T. I I NECEIVING FROCESS   |                                        |               |

# iMQ Technology Inc.

| No.: TDDS01-S7615-EN | Name: SQ7615 Datasheet | Version: V1.3 |

|----------------------|------------------------|---------------|

|                      |                        |               |

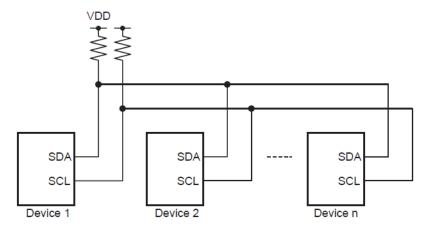

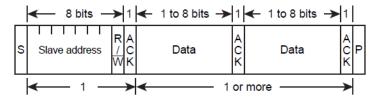

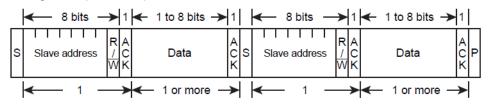

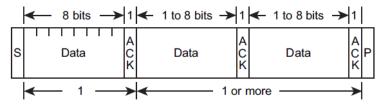

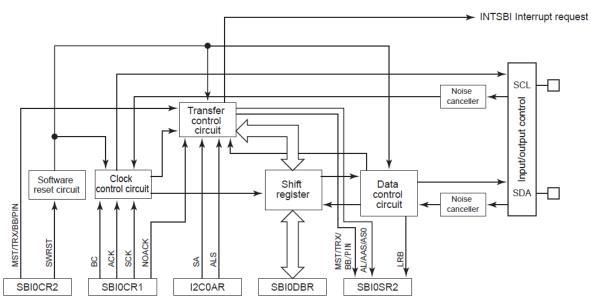

| 15. SERIAL BUS INTERFACE(SBI)/I2C                                                      | 277         |

|----------------------------------------------------------------------------------------|-------------|

| 15.1 COMMUNICATION FORMAT                                                              |             |

| 15.1.1 I2C bus                                                                         | 277         |

| 15.1.2 Free data format                                                                | 278         |

| 15.2 CONFIGURATION                                                                     | 279         |

| 15.3 Control                                                                           | 280         |

| 15.4 FUNCTIONS                                                                         | 286         |

| 15.4.1 Low power consumption function                                                  | 286         |

| 15.4.2 Selecting the slave address match detection and the GENERAL CALL de             | tection 286 |

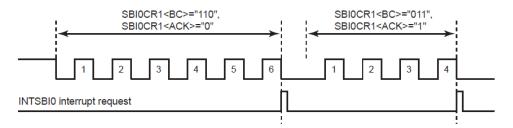

| 15.4.3 Selecting the number of clocks for data transfer and selecting the acknowledge. |             |

| ment or non-acknowledgement mode                                                       |             |

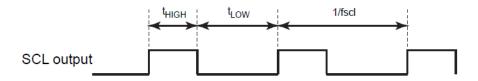

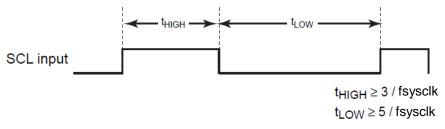

| 15.4.4 Serial clock                                                                    | 290         |

| 15.4.5 Master/slave selection                                                          | 292         |

| 15.4.6 Transmitter/receiver selection                                                  |             |

| 15.4.7 Start/stop condition generation                                                 | 293         |

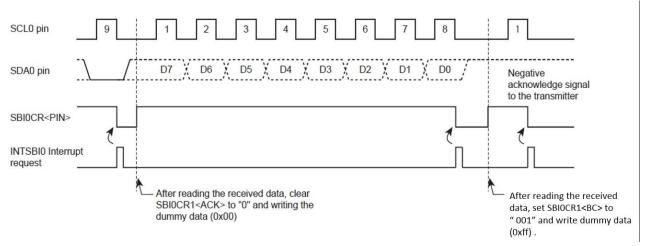

| 15.4.8 Interrupt service request and release                                           | 294         |

| 15.4.9 Setting of serial bus interface mode                                            |             |

| 15.4.10 Software reset                                                                 |             |

| 15.4.11 Arbitration lost detection monitor                                             | 295         |

| 15.4.12 Slave address match detection monitor                                          | 297         |

| 15.4.13 GENERAL CALL detection monitor                                                 | 297         |

| 15.4.14 Last received bit monitor                                                      |             |

| 15.4.15 Slave address and address recognition mode specification                       | 299         |

| 15.5 I2C Data transfer of I2C Bus                                                      |             |

| 15.5.1 Device initialization                                                           | 299         |

| 15.5.2 Start condition and slave address generation                                    | 299         |

| 15.5.3 1-word data transfer                                                            |             |

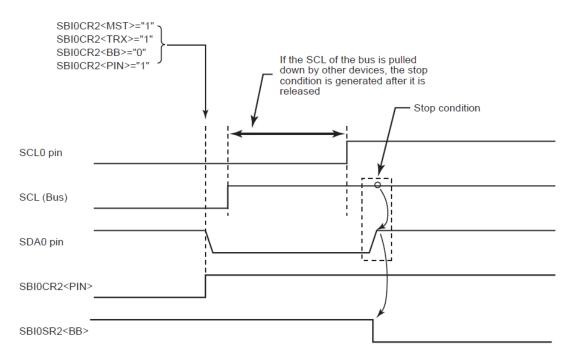

| 15.5.4 Stop condition generation                                                       | 305         |

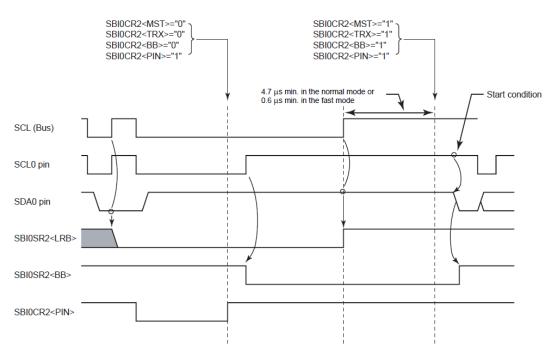

| 15.5.5 Restart                                                                         |             |

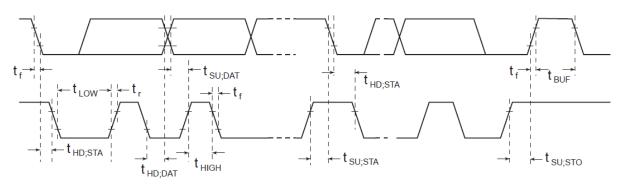

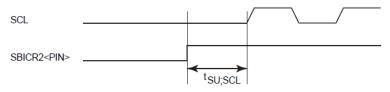

| 15.6 AC Specifications                                                                 | 308         |

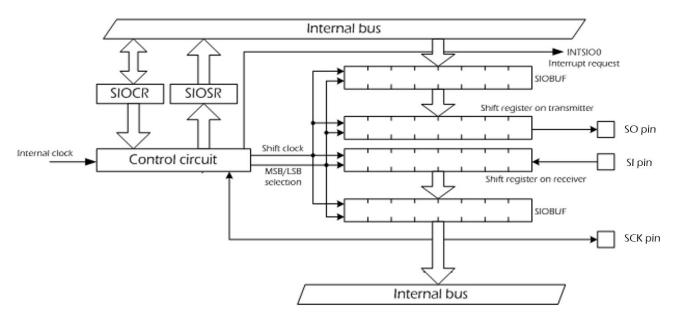

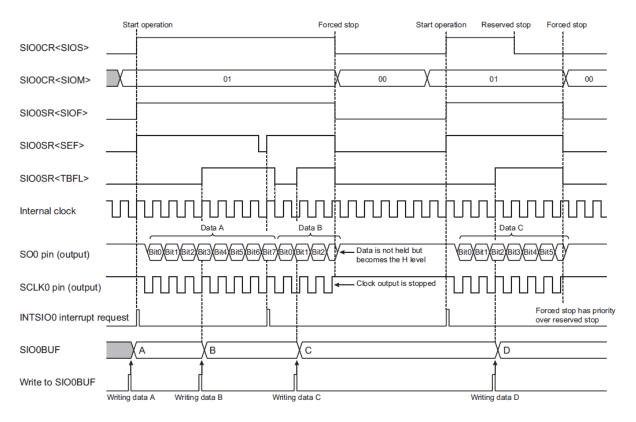

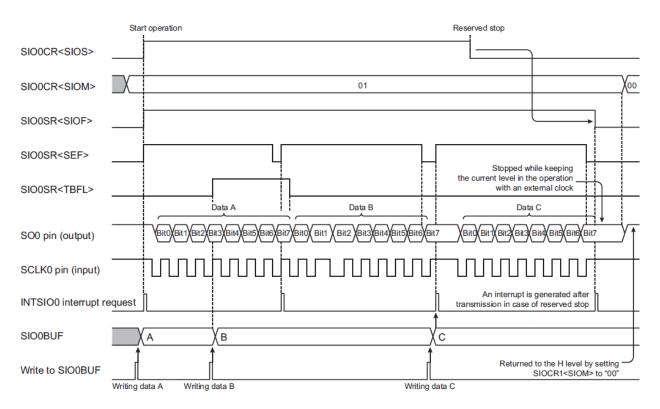

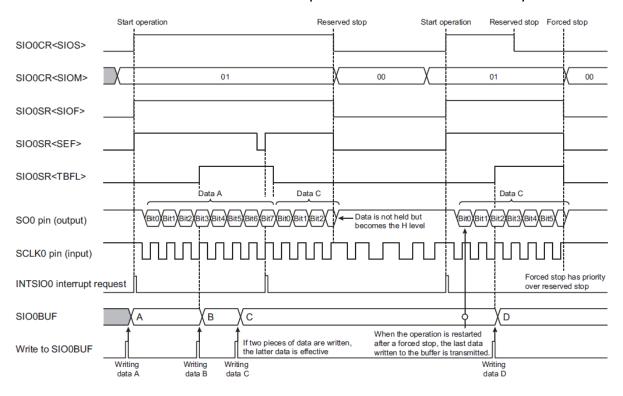

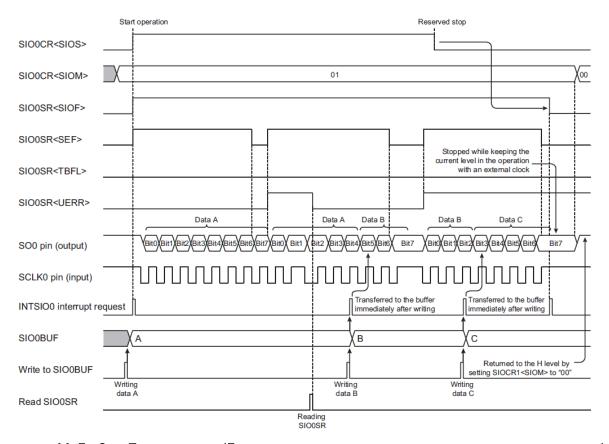

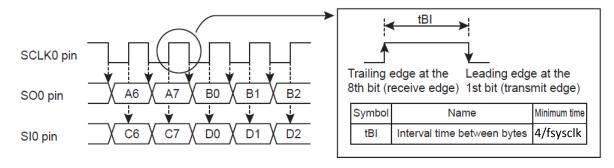

| 16 SYNCHRONOUS SERIAL INTERFACE (SIO)                                                  | 310         |

| 16.1 Configuration                                                                     | 310         |

| 16.2 Control                                                                           | 311         |

| 16.3 Low power consumption function                                                    | 315         |

| 16.4 Functions                                                                         |             |

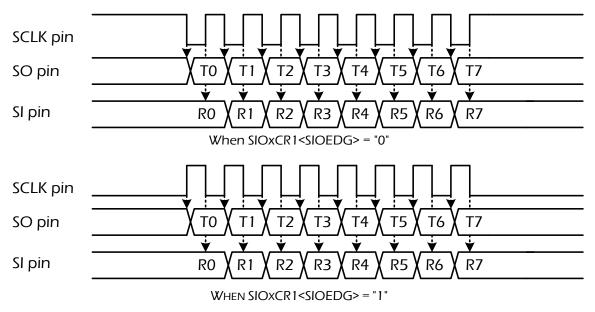

| 16.4.1 Transfer format                                                                 | 316         |

| 16.4.2 Serial clock                                                                    |             |

| 16.4.3 Transfer edge selection                                                         | 317         |

| 16.5 Transfer Modes                                                                    |             |

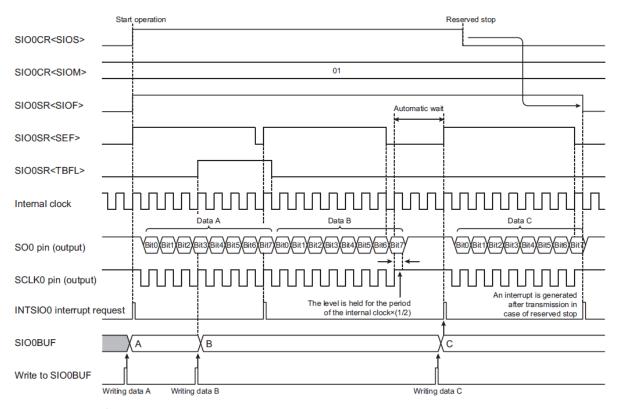

| 16.5.1 8-bit transmit mode                                                             | 319         |

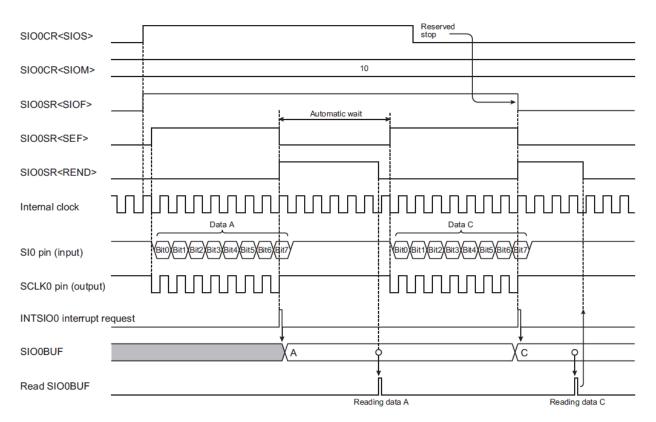

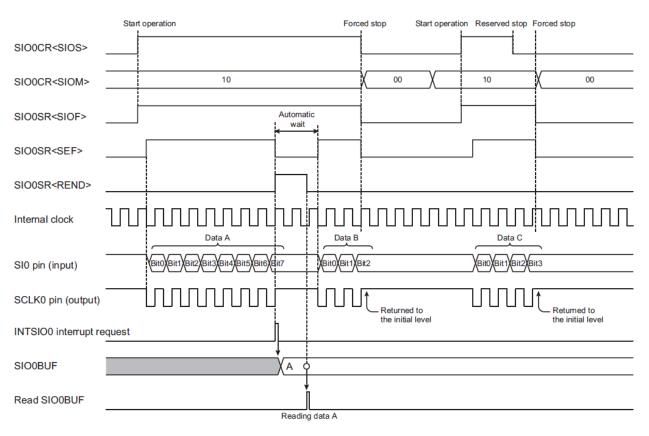

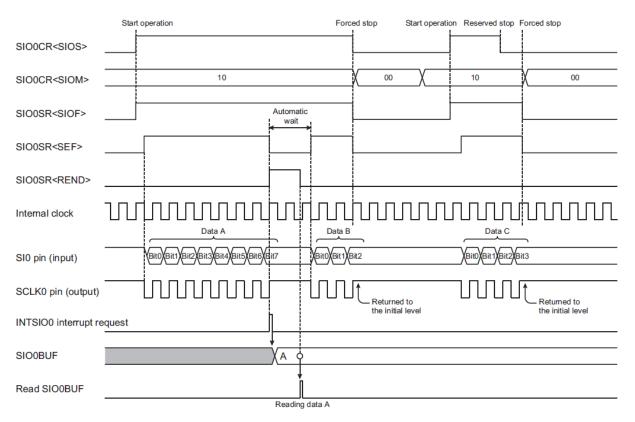

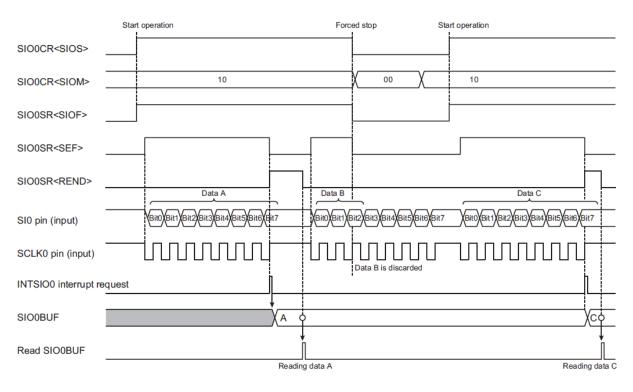

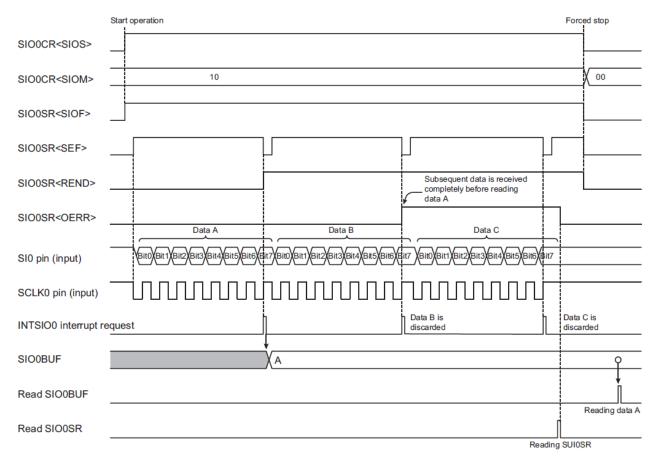

| 16.5.2 8-bit Receive Mode                                                              |             |

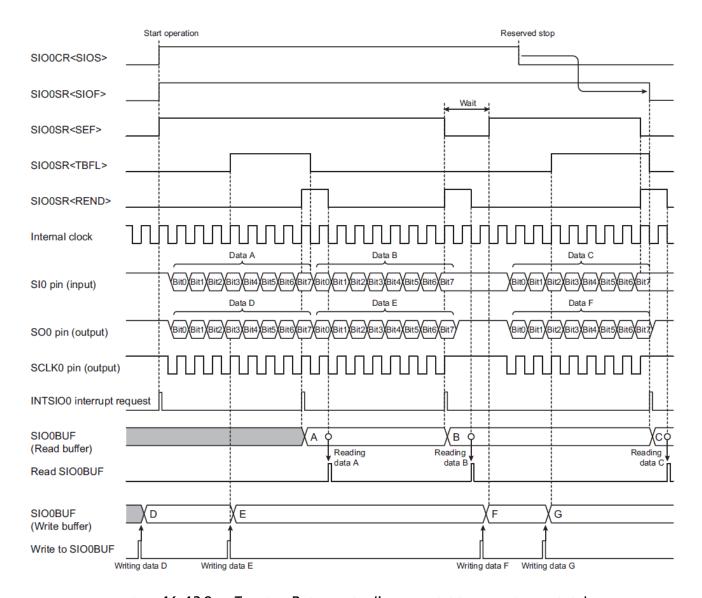

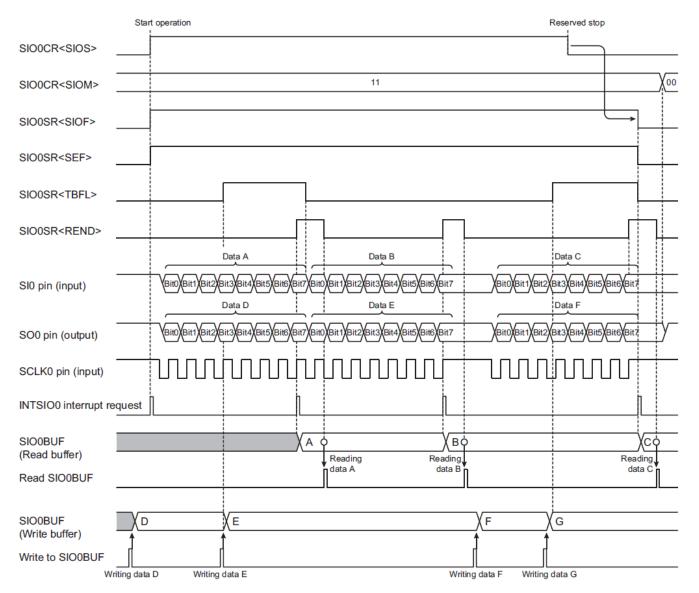

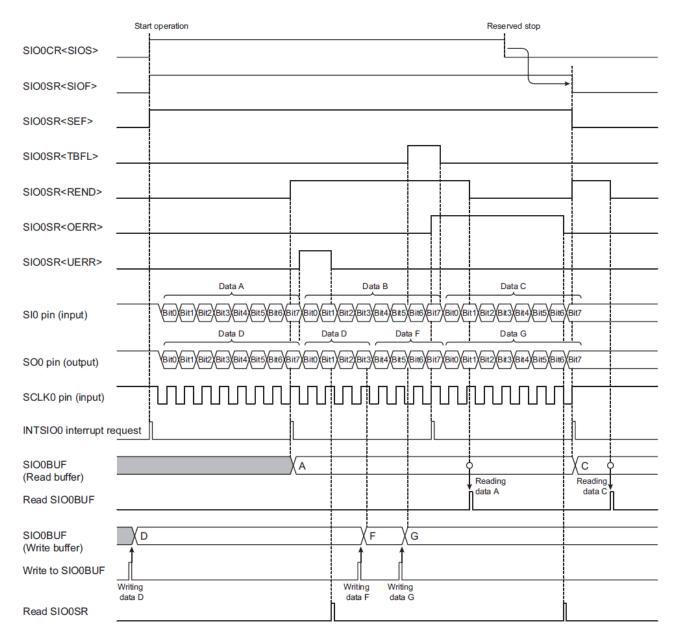

| 16.5.3 8-bit Transmit/receive mode                                                     | 331         |

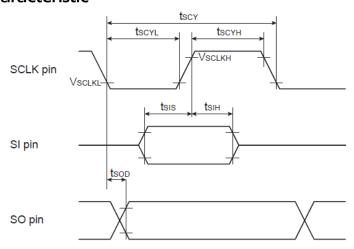

| 16.6 AC CHARACTERISTIC                                                                 |             |

| 17 SECURITY                                                                            |             |

| 17. 1 Cyclic Redundancy Check (CRC)                                                    | 338         |

| 17.1.1 Function                                                                        |             |

| 17. 1.2 Control                                                                        | 338         |

Page: 6 / 352

iMO reserves the right to change the information in this document without prior notice. Please contact iMO to obtain the latest version of product specification before placing your order. Use of iMO devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMO from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7615-EN

### iMQ Technology Inc.

| 17. 2 Data Integrity Check (DIC)       | 341 |

|----------------------------------------|-----|

| 17.2.1 DIC Function                    |     |

| 17.2.2 DIC Control                     | 342 |

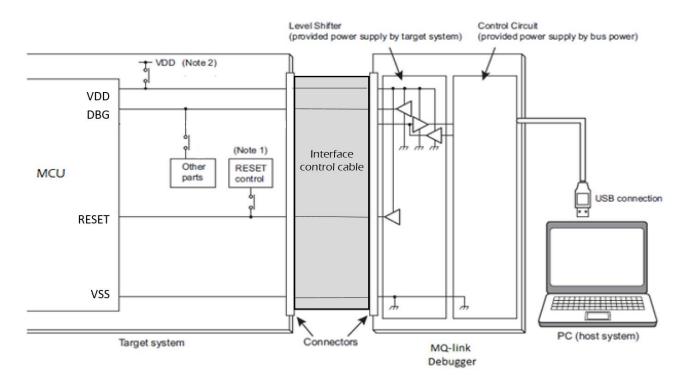

| APPENDIX A. ON-CHIP DEBUG              |     |

| APPENDIX B. PRODUCT NUMBER INFORMATION |     |

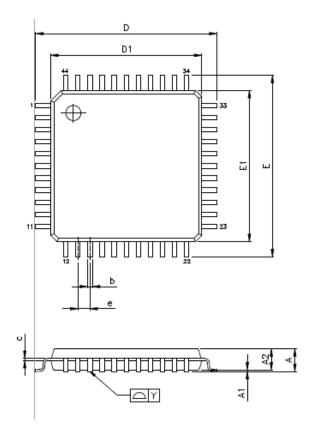

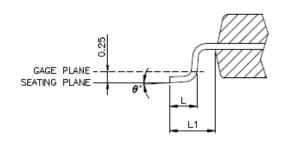

| APPENDIC C. PACKAGE DIMENSIONS         | 348 |

APPENDIX D. APPLICATION NOTICE.......349

Name: SQ7615 Datasheet

Version: V1.3

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

# 1. Change History

| Version | Approved<br>Date | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V 1.0   | 2019/09/05       | English Version first issued.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| V 1.1   | 2019/11/4        | <ol> <li>Modify "2.1 Feature" and "3.3 D.C. characteristics"</li> <li>Modify "figure 5-1" and "5.1.1 system control register"</li> <li>Modify "10. I/O Ports(P0DO and P2DO description)"</li> <li>Update "8.1.9.1 One-Shot Mod" ang "figure 8-4"</li> <li>Modify "9.1 Function"</li> <li>Update "12. Pheripheral Network Inter-Connect".</li> <li>Modify "15.3 Control (SBIxCR1)"</li> <li>Add "Appendix C.(LOFP32)"</li> <li>Update "Appendix D.(A/E/G/H)"</li> </ol> |  |

| V 1.2   | 2020/3/16        | <ol> <li>Add "2.4 Pin assignment/Description(KWI andEINT)"</li> <li>Add "6.2.4 Device Initialization table 6-3"</li> <li>Add "6.8 System Power Monitor"</li> <li>Update "figure 8-1 note description"</li> <li>Update "12. Pheripheral Network Inter-Connect"</li> <li>Update "14.6 Transfer Baud Rate",add 24 MHz/12 MHz data.</li> <li>Update "16.4.2 Serial Clock(table 16-2 "flclk")</li> <li>Add "Appendix D. © CLKCR1<hircen>=1"</hircen></li> </ol>             |  |

| V1.3    | 2020/4/6         | 1.Update "9. Flash Memory Controller", remove 2-bytes description.<br>2.Update "16.4.2 Serial Clock": slave mode maximum frequency is 4MHz, and table 16-2.<br>3." 16.6 AC Characteristic", add the note for tsysclk.                                                                                                                                                                                                                                                  |  |

Name: SQ7615 Datasheet Version: V1.3 No.: TDDS01-S7615-EN

# 2. Product Overview

#### 2.1 Features

#### **Basic Information**

Operating voltage: 2.0V ~ 5.5V

Operating temperature: -40°C ~ 85°C

- Max system frequency 24 MHz

- Instruction set is compatible with Toshiba TLCS-870/C1

#### **Memory Configuration**

- 64 KB Flash

- 4 KB RAM

#### **Operation modes**

- Normal mode: 150 uA/MHz @ 3.3V

- Deep sleep mode: 1 uA @ 3.3V, ,RTC disable, CPU and RAM are retained

- Deep sleep mode: 1.6uA@3.3V, RTC enable,LXTAL on,CPU and RAM are retained.

#### **Clock Source**

- 16 MHz external crystal(high frequency)

- 32 kHz external crystal (low frequency)

- PLL

- Internal crystal:

- 32 kHz

- 16 MHz

#### I/O

- 41 I/Os

- 3 sets UART · 2 sets I2C and 2 sets SIO

#### Multiplier and Dividor

- 16 x16-bit ,multiplication,and 32-bit addition

- 32-bit divid 32-bit

#### Timer/Counter

- 8 16-bit timer/counter · Timer, External trigger, Event counter, Window, Pulse width measurement, PPG output modes

- RTC

- Watch-dog timer

#### External interrupt

8 external interrupt input (EINT0~EINT7)

#### 12-bit ADC

- 12 CH ADC input

- **ADC VREF**

#### Low voltage detection (LVD), total 8 levels.

2.0V/2.35V/2.65V/2.85V/3.15V/3.98V/4.2V /4.5V

#### Brown-out reset (BROR), total 4 levels

- 1.9V/2.25V/2.55V/2.75V

- **Code Protection**

#### Package type

LQFP 44(10x10)

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

#### 2.2 Preface

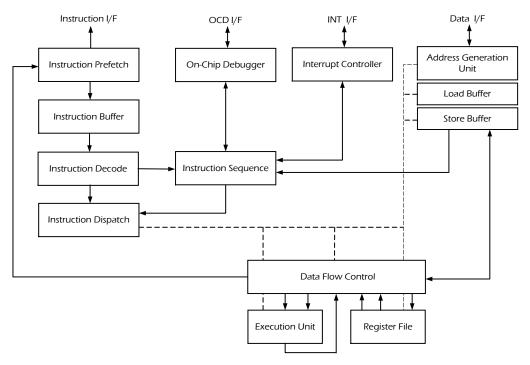

SQ7615 is 870E core which is an energy efficient and low gate count core that implements the Toshiba TLCS-870/C1 CISC instruction set architecture. The variable length instruction set offers 38 core instructions, nine addressing modes and powerful memory manipulation operations. The smallest instructions have one-byte opcode and largest instruction five bytes. Instructions that are frequently used have two- to four-byte opcodes.

870E core is a three-stage execution pipeline design. The instruction queue and the core functional units are capable of executing frequently used instructions in a single cycle. The Harvard memory architecture allows simultaneous instruction fetch and data access. Dedicated hardware is designed to handle instruction and data alignment, eliminating software alignment overhead.

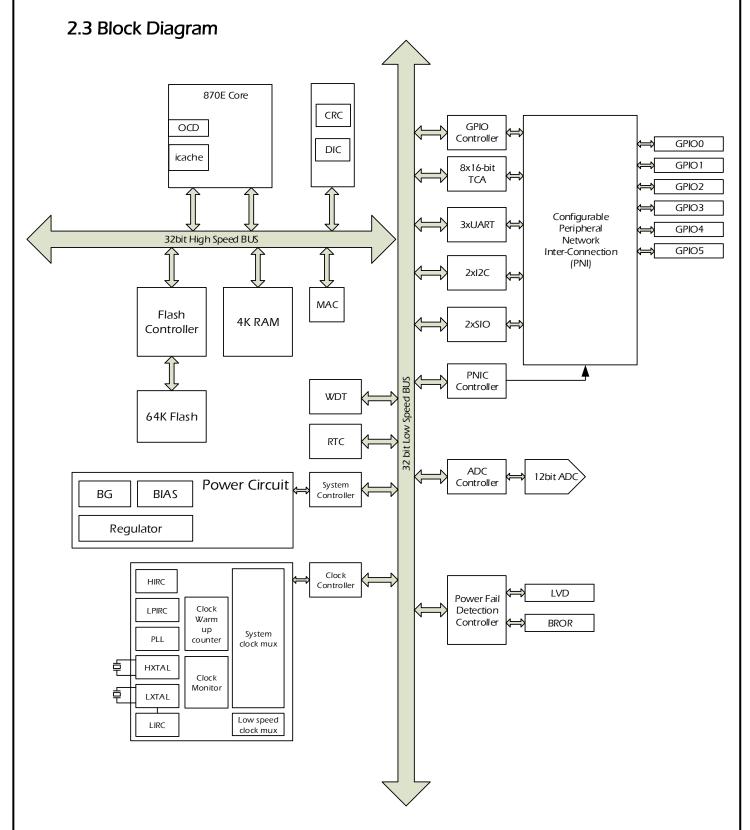

SQ7615 has 64K Bytes flash mamery, 4K Bytes RAM, various I/Os funcitons, timers/counters, and 12-bit ADC. There are variety of internal clock and external clock sources; different digital peripheral, and accurate analog features. User can optimize by different requirements.

FIGURE 2- 1 MQ870E Block Diagram

Page: 10 / 352

### iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

| Product no.                                        | SQ7615LA044SETR                                                   |

|----------------------------------------------------|-------------------------------------------------------------------|

| Pin count.<br>(IOs)                                | 44<br>(41)                                                        |

| Operating voltage                                  | 2.0~5.5V                                                          |

| Operating temp.                                    | -40~85C                                                           |

| Flash size /(number of guaranteed writes to flash) | 64K Bytes/100,000 times                                           |

| RAM                                                | 4K Bytes                                                          |

| ADC                                                | 12-bit x 12-CH<br>(VDD,Vref)                                      |

| Key-on wake up                                     | 8                                                                 |

| Interrupt                                          | External: 8<br>Internal: 29                                       |

| HIRC /<br>Accuracy                                 | 16MHz<br>+/- 1% @ 0~50C<br>+/- 1.5% @ -20~70C<br>+/- 3% @ -40~85C |

| External Oscillator                                | 1~16MHz or 32768Hz                                                |

| BROR                                               | 4 levels                                                          |

| LVD                                                | 8 levels<br>(+/- 3%)* <sup>2</sup>                                |

| Timers/                                            | 16bit x 8                                                         |

| Counters                                           | WDT,TBT,RTC                                                       |

| PWM/PPG                                            | 16bit x 8                                                         |

| Communication                                      | UART x 3,<br>SIO x 2,<br>I2C x 2                                  |

| On-chip debug                                      | Yes                                                               |

| Package type                                       | LOFP44                                                            |

Note 1:"VDD" indicates that the ADC uses VDD as the internal reference voltage; "Vref" indicates that the ADC uses an external reference

Note 2: SQ products has 8 levels LVD; the LVD accuracy can be ±3%. The detail please refer chapter "3.6 LVD characters.".

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

FIGURE 2-2 SQ7615 BLOCK DIAGRAM

Page: 12 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7615-EN | Name: SQ7615 Datasheet | Version: V1.3

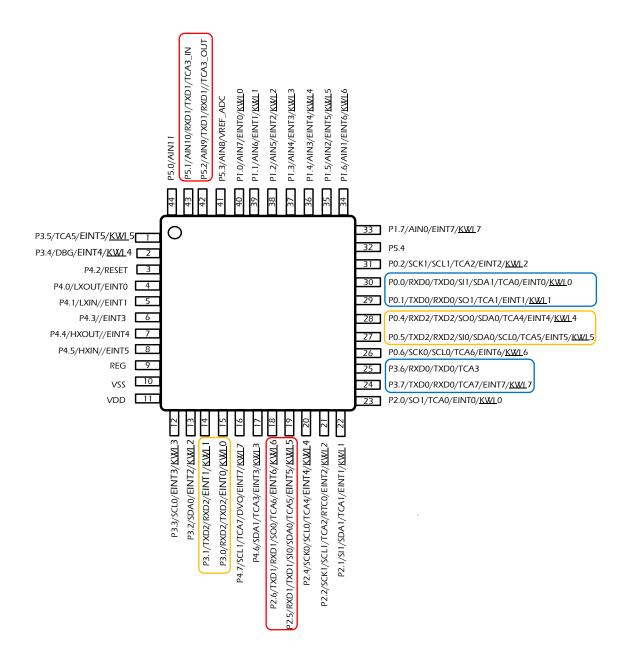

# 2.4 Pin Assignment/Description

FIGURE 2-3 PIN ASSIGNMENT OF SQ7615 LQFP-44

Note 1: SQ7615 support 4-wire emulation. User has to connect to P3.4/DBG, P4.2/RESET, VDD, GND under emulation. Suggest to reserve the emulation pins in the system board. Figure 2-4, Figure 2-6 are reference circuits, other components added may affect emulation or function performance.

Note 2: SQ7615 can be programming (by writer) by below two type programming pins. Suggest to reserve the programming pins in the system board. Figure 2-4, Figure 2-6 are reference circuits, other components added may affect programming performance or functions.

Page: 13 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

- (a) 4-wire OCDE Mode: the 4-wire OCDE pins are same as emulation pins (P3.4/DBG \ P4.2/RESET \ VDD \ VSS). The OCDE programming time for 64Kbyte memory is around 16 seconds. iMQ MQ-Link and Flash Writer both suppot 4-wire OCDE programming.

- (b) Bootloader: Bootloader pins are P0.0/ISPSI \ P0.1/ISPSO \ P0.2/ISPSCK \ VDD \ VSS. The Bootlader programming time for 64K byte memory is around 8 seconds. iMQ Flash Writer can suppot bootloader programming.

Note 3: TCAx support Input/output, only TCA3 is exception. P5.1/TCA3\_IN supports input only, and P5.2/TCA3\_OUT supports output only.

Note 4: UART / I2C/ SIO pins need to be paired as below. For example: if select P0.0 as RXD0, and P0.1 has to be TXD0.

| UART0 | TXD0/RXD0 | P0.0/RXD0/TXD0<br>P0.1/TXD0/RXD0 | P3.6/RXD0/TXD0<br>P3.7/TXD0/RXD0 |

|-------|-----------|----------------------------------|----------------------------------|

| UART1 | TXD1/RXD1 | P2.5/RXD1/TXD1<br>P2.6/TXD1/RXD1 | P5.1/RXD1/TXD1<br>P5.2/TXD1/RXD1 |

| UART2 | TXD2/RXD2 | P0.4/RXD2/TXD2<br>P0.5/TXD2/RXD2 | P3.0/RXD2/TXD2<br>P3.1/TXD2/RXD2 |

| I2C0 | SCL0/SDA0 | P0.6/SCL0<br>P0.5/SDA0 | P0.5/SCL0<br>P0.4/SDA0 | P2.4/SCL0<br>P2.5/SDA0 | P3.3/SCL0<br>P3.2/SDA0 |

|------|-----------|------------------------|------------------------|------------------------|------------------------|

| I2C1 | SCL1/SDA1 | P0.2/SCL1<br>P0.0/SDA1 | P2.2/SCL1<br>P2.1/SDA1 | P4.7/SCL1<br>P4.6/SDA1 |                        |

|      |                | P0.6/SCK0  | P2.4/SCLK1  |

|------|----------------|------------|-------------|

| SIO0 | SCK0/ SI0/ SO0 | P0.5/SI0   | P2.5/SI0    |

|      | , ,            | P0.4/SO0   | P2.6/ SO0   |

|      |                | P0.2/SCLK1 | P2.2/ SCLK1 |

| SIO1 | SCK1/SI1 / SO1 | P0.0/SI1   | P2.1/ SI1   |

|      |                | P0.1/SO1   | P2.0/ SO1   |

|      |      | Pin Name |              |       | Pin/Port      | function           |

|------|------|----------|--------------|-------|---------------|--------------------|

|      |      | Pin Name | 3            |       | Key-on Wakeup | External Interrupt |

| P0.0 | P1.0 | P2.0     | P3.0         |       | <u>KWI</u> 0  | EINT0              |

| P0.1 | P1.1 | P2.1     | P3.1         |       | <u>KWI</u> 1  | EINT1              |

| P0.2 | P1.2 | P2.2     | P3.2         |       | <u>KWI</u> 2  | EINT2              |

| -    | P1.3 | -        | P3.3<br>P3.6 | P4.6  | <u>KWI</u> 3  | EINT3              |

| P0.4 | P1.4 | P2.4     | P3.4         |       | <u>KWI</u> 4  | EINT4              |

| P0.5 | P1.5 | P2.5     | P3.5         |       | <u>KWI</u> 5  | EINT5              |

| P0.6 | P1.6 | P2.6     | -            | -     | <u>KWI</u> 6  | EINT6              |

| -    | P1.7 | -        | P3.7         | P4.7  | <u>KWI</u> 7  | EINT7              |

|      |      |          |              | P4.0  |               | EINT0              |

|      |      |          |              | P4.1  |               | EINT1              |

|      |      |          |              | P4.2  |               | EINT2              |

|      |      |          |              | P4.3- |               | EINT3              |

|      |      |          |              | P4.4  |               | EINT4              |

|      |      |          |              | P4.5  |               | EINT5              |

TABLE 2- 1 I/Os,KWI, EXTERNAL INTERRUPT TABLE

Page: 14/ 352

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

| 44-Pin<br>No. | Pin Name/ Pin Option   | I/O Type        | Function Description                                                                                                                                                                                                                                 |

|---------------|------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | P3.5/ TCA5/EINT5/KWI 5 | I/O<br>(Type A) | P3.5 is bi-directional I/O pin, which are software configurable to be with pull-up or pull-down resistors.  16-bit timer pin TCA5, external interrupt EINT5, and wake up pin KWI 5 are pin-shared with P3.5.                                         |

| 2             | P3.4/ DBG/EINT4/KWI 4  | I/O<br>(Type A) | P3.4 is bi-directional I/O pin, which are software configurable to be with pull-up or pull-down resistors.  OCDE pin DBG, external interrupt EINT4, and wake up pin KWI 4 are pin-shared with P3.4.                                                  |

| 3             | P4.2/RESET /EINT2      | I/O<br>(Type A) | P10 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors  RESET and external interrupt EINT2 are pin-shared with P4.2.  RESET is low-active.                                                        |

| 4             | P4.0/LXOUT /EINT0      | I/O<br>(Type B) | P4.0 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  LXOUT and external interrupt EINTO are pin-shared with P4.0. LXOUTis connected to a low frequency external crystal for system clock.    |

| 5             | P4.1/LXIN /EINT1       | I/O<br>(Type B) | P4.1 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  LXIN and external interrupt EINT1 are pin-shared with P4.1.  LXIN is connected to a low frequency external crystal for system clock.    |

| 6             | P4.3 /EINT3            | I/O<br>(Type A) | P4.3 is bi-directional I/O pin, which are software configurable to be with pull-up or pull-down resistors.  External interrupt EINT3 is pin-shared with P4.3.                                                                                        |

| 7             | P4.4/HXOUT /EINT4      | I/O<br>(Type B) | P4.4 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  HXOUT and external interrupt EINT4 are pin-shared with P4.4.  HXOUT is connected to a high frequency external crystal for system clock. |

| 8             | P4.5/HXIN/ /EINT5      | I/O<br>(Type B) | P4.5 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  HXIN and external interrupt EINT5 are pin-shared with P4.5.  HXIN is connected to a high frequency external crystal for system clock.   |

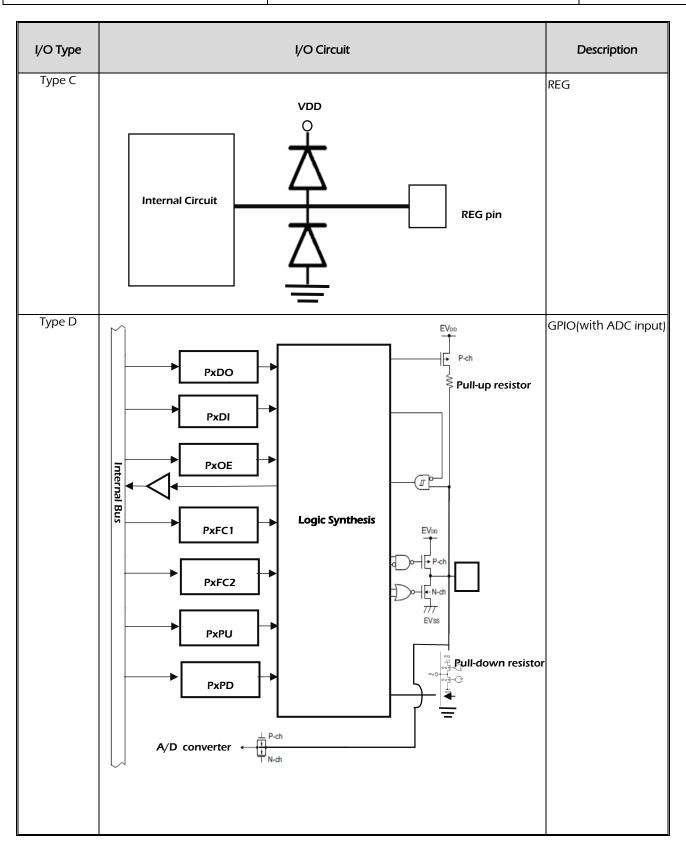

| 9             | REG                    | (Type C)        | Pin for connecting regulator output stabilization capacitance for internal operation. Connect the REG pin to VSS via a capacitor 1uF  Note: REG pin cannot supply to external circuit.                                                               |

| 10            | vss                    | GND             | Ground                                                                                                                                                                                                                                               |

Page: 15 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

iMQ Technology Inc.

No.: TDDS01-S7615-EN Version: V1.3 Name: SQ7615 Datasheet

| 44-Pin<br>No. | Pin Name/ Pin Option                         | I/O Type        | Function Description                                                                                                                                                                                                                                                                   |

|---------------|----------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11            | VDD                                          | Power           | Positive power supply                                                                                                                                                                                                                                                                  |

| 12            | P3.3/SCL0/EINT3/KWI3                         | I/O<br>(TypeA)  | P3.3 is bi-directional I/O pins, which are software configurable to be with pull-up or pull-down resistors.  SCLO( I2C bus clock input/output 0), external interrupt EINT3, and wake up pin KWI 3 are pin-shared with P3.3.                                                            |

| 13            | P3.2/SDA0/EINT2/KWI2                         | I/O<br>(Type A) | P3.2 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SDA0 (I2C bus data input/output 0), external interrupt  EINT2, and wake up pin KWI 2 are pin-shared with P3.2                                                             |

| 14            | P3.1/TXD2/RXD2/EINT1/KWI1                    | I/O<br>(Type A) | P3.1 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART TXD2/RXD2, external interrupt EINT1, and wake up pin KWI 1 are pin shared with P3.1.                                                                                 |

| 15            | P3.0/RXD2/TXD2/ EINT0/KWI0                   | I/O<br>(Type A) | P3.0 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART RXD2/TXD2, external interrupt EINTO, and wake up pin KWI 0 are pin shared with P3.0.                                                                                 |

| 16            | P4.7/SCL1/TCA7 /DVO/EINT7<br>/KWI7           | I/O<br>(Type A) | P4.7 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SCL1(I2C bus clock input/output 0), 16-bit timer pin TCA7,DVO, external interrupt EINT7, and wake up pin KWI 7 are pin-shared with P4.7.                                  |

| 17            | P4.6/SDA1/TCA3/EINT3 /KWI3                   | I/O<br>(Type A) | P4.6 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SDA1 (I2C bus data input/output 0), 16-bit timer pin TCA3, external interrupt EINT3, and wake up pin KWI 3 are pin-shared with P4.6                                       |

| 18            | P2.6/TXD1/RXD1/SO0/TCA6/EIN<br>T6 /KWI6      | I/O<br>(Type A) | P2.6 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART TXD1/RXD1, SO0 (serial data output 0), 16-bit timer pin TCA6, external interrupt EINT6, and wake up pin KWI 6 are pin-shared with P2.6                               |

| 19            | P2.5/RXD1/TXD1/SI0/SDA0/TCA<br>5/EINT5 /KWI5 | I/O<br>(Type A) | P2.5 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART RXD1/TXD1, SI0(serial data input 0), SDA0 ( I2C bus data input/output 0),16-bit timer pin TCA5, external interrupt EINT5, and wake up pin KWI 5 are pin-shared P2.5. |

| 20            | P2.4/SCK0/SCL0/TCA4/EINT4<br>/KWI4           | I/O<br>(Type A) | P2.4 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SCKO (Serial clock input/output 0), SCLO( I2C bus clock input/output 0), 16-bit timer pin TCA4, external interrupt EINT4, and wake up pin KWI 4 are pin-shared P2.4.      |

Page: 16 / 352 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

iMQ Technology Inc.

No.: TDDS01-S7615-EN Version: V1.3 Name: SQ7615 Datasheet

| 44-Pin<br>No. | Pin Name/ Pin Option                              | I/O Type        | Function Description                                                                                                                                                                                                                                                                                                            |

|---------------|---------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21            | P2.2/SCK1/SCL1/TCA2/RTC0/EIN<br>T2 /KWI2          | I/O<br>(Type A) | P2.2 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SCK1 (Serial clock input/output 1), SCL1 (I2C bus clock input/output 1),16-bit timer pin TCA2, RTC0, external interrupt EINT2, and wake up pin KWI 2 are pin-shared P2.2.                                          |

| 22            | P2.1/SI1/SDA1/TCA1/EINT1<br>/KWI1                 | I/O<br>(Type A) | P2.1 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors. SI1(serial data input 1), SDA1 (I2C bus data input/output 1) 16-bit timer pin TCA1, external interrupt EINT1, and wake up pin KWI 1 are pin-shared P2.1.                                                            |

| 23            | P2.0/SO1/TCA0/EINT0 /KWI0                         | I/O<br>(Type A) | P2.0 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SO1 (serial data output 1),16-bit timer pin TCA0, external interrupt EINTO, and wake up pin KWI 0 are pin-shared with P2.0.                                                                                        |

| 24            | P3.7/TXD0/RXD0/TCA7/EINT7<br>/KWI7                | I/O<br>(Type A) | P3.7 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART TXD0/RXD0, 16-bit timer pin TCA7, external interrupt EINT7, and wake up pin KWI7 are pin-shared with P3.7                                                                                                     |

| 25            | P3.6/RXD0/TXD0/TCA3/EINT3<br>/KWI3                | I/O<br>(Type A) | P3.6 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART RXD0/TXD0 , 16-bit timer pin TCA3, external interrupt EINT3, and wake up pin KWI 3 are pin-shared with P3.6                                                                                                   |

| 26            | P0.6/SCK0/SCL0/TCA6/EINT6<br>/KWI6                | I/O<br>(Type A) | P0.6 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SCK0 (Serial clock input/output 0), SCL0( I2C bus clock input/output 0), 16-bit timer pin TCA6, external interrupt EINT6, and wake up pin KWI 6 are pin-shared P0.6                                                |

| 27            | P0.5/TXD2/RXD2/SI0/SDA0/SCL0<br>/TCA5/EINT5 /KWI5 | I/O<br>(Type A) | P0.5 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART TXD2/RXD2, SI0(serial data input 0), SDA0 ( I2C bus data input/output 0), SCL0( I2C bus clock input/output 0), 16-bit timer pin TCA5, external interrupt EINT5, and wake up pin KWI5 are pin-shared with P0.5 |

| 28            | P0.4/RXD2/TXD2/SO0/SDA0/TC<br>A4/EINT4 /KWI4      | I/O<br>(Type A) | P0.4 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART RXD2/TXD2, SO0 (serial data output 0) SDA0 (I2C bus data input/output 0), 16-bit timer pin TCA4, external interrupt EINT4, and wake up pin KWI 4 are pin-shared with P0.4                                     |

iMQ Technology Inc.

No.: TDDS01-S7615-EN Version: V1.3 Name: SQ7615 Datasheet

| 44-Pin | Pin Name/ Pin Option                                       | I/O Type              | Function Description                                                                                                                                                                                                                                                                                     |

|--------|------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.    | Option                                                     | , 5 1,50              | i i                                                                                                                                                                                                                                                                                                      |

| 29     | P0.1/TXD0/RXD0/SO1/TCA1/<br>EINT1 /KWI1/ISPTxD / ISPSO     | I/O<br>(Type A)       | P0.1 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART TXD0/RXD0, SO1 (serial data output 1), 16-bit timer pin TCA1, external interrupt EINT1, wake up pin KWI 1, and ISPTxD/ ISPSO are pin-shared with P0.1                                  |

| 30     | P0.0/RXD0/TXD0/SI1/SDA1/TCA0/<br>EINT0 /KWI0/ ISPRxD/ISPSI | I/O<br>(Type A)       | P0.0 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  UART RXD0/TXD0, SI1 (serial data input 1), SDA1 (I2C bus data input/output 1), 16-bit timer pin TCA0, external interrupt EINTO, wake up pin KWIO and ISPRxD/ISPSI are pin-shared with P0.0. |

| 31     | P0.2/ SCK1/SCL1/TCA2/ EINT2<br>/KWI2/ISPSCK                | I/O<br>(Type A)       | P0.2 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  SCK1 (Serial clock input/output 1), SCL1(I2C bus clock input/output 1),16-bit timer pin TCA2, external interrupt EINT2, wake up pin KWI2, and ISPSCK are pin-shared with P0.2.              |

| 32     | P5.4                                                       | I/O<br>(Type A)       | P5.4 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.                                                                                                                                                                                              |

| 33     | P1.7/AIN0// EINT7 /KWI7                                    | (Type A) I/O (Type D) | P1.7 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AINO, external interrupt EINT7, wake up pin KWI 7, are pin-shared with P1.7                                                                                                       |

| 34     | P1.6/AIN1/ EINT6 /KWI6                                     | I/O<br>(Type D)       | P1.6 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN1, external interrupt EINT6, and wake up pin KWI 6, are pin-shared with P1.6.                                                                                                  |

| 35     | P1.5/AIN2/ EINT5 /KWI5                                     | I/O<br>(Type D)       | P1.5 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN2, external interrupt EINT5, and wake up pin KWI 5 are pin-shared with P1.5.                                                                                                   |

| 36     | P1.4/AIN3/ EINT4 /KWI4                                     | I/O<br>(Type D)       | P1.4 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors. ADC input AIN3, external interrupt EINT4, and wake up pin KWI 4 are pin-shared with P1.4.                                                                                                    |

| 37     | P1.3/AIN4/ EINT3 /KWI3                                     | I/O<br>(Type D)       | P1.3 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN4, external interrupt EINT3, and wake up pin KWI3 are pin-shared with P1.3.                                                                                                    |

| 38     | P1.2/AIN5/ EINT2 /KWI2                                     | I/O<br>(Type D)       | P1.2 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN5, external interrupt EINT2, and wake up pin KWI2 are pin-shared with P1.2.                                                                                                    |

| 39     | P1.1/AIN6/ EINT1 /KWI1                                     | I/O<br>(Type D)       | P1.1 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN6, external interrupt EINT1, and wake up pin KWI1 are pin-shared with P1.1.                                                                                                    |

Page: 18 / 352 iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

#### iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

| 44-Pin<br>No. | Pin Name/ Pin Option             | I/O Type/       | Function Description                                                                                                                                                                                  |

|---------------|----------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40            | P1.0/AIN7/ EINTO /KWI0           | I/O<br>(Type D) | P1.0 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN7, external interrupt EINT0, and wake up pin KWI0 are pin-shared with P1.0. |

| 41            | P5.3/AIN8/VREF_ ADC              | I/O<br>(Type D) | P5.3 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN8 and VREF_ADC is pin-shared with P5.3.                                     |

| 42            | P5.2/AIN9/TXD1/RXD1/TCA3_OU<br>T | I/O<br>(Type D) | P5.2 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN9, UART TXD1/RXD1 ,and 16-bit timer pin TCA3_OUT are pin-shared with P5.2.  |

| 43            | P5.1/AIN10/TXD1/RXD1/TCA3_IN     | I/O<br>(Type D) | P5.1 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN10, UART TXD1/RXD1, and 16-bit timer pin TCA3_IN are pin-shared with P5.1.  |

| 44            | P5.0/AIN11                       | I/O<br>(Type D) | P5.0 is a bi-directional I/O pin, which is software configurable to be with pull-up or pull-down resistors.  ADC input AIN11, UART TXD1/RXD1, and 16-bit timer pin-TCA3_IN-is pin-shared with P5.0.   |

Note 1 For emulation, user has to connect to P3.4/DBG, P4.2/RESET, VDD, GND.

Recommended external application circuits as below figures, please follow the recommendation to design.

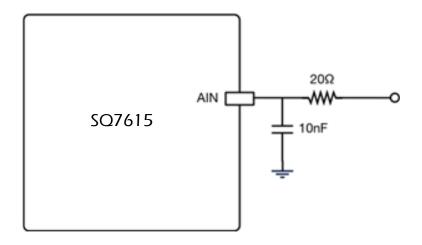

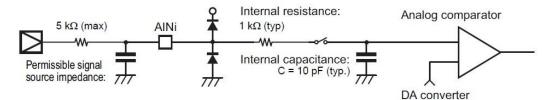

# 1. ADC Input Filter:

# **ADC Input Filter**

FIGURE 2-4 SQ7615 RECOMMENDED EXTERNAL APPLICATION CIRCUITS (ADC INPUT FILTER)

Page: 19 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

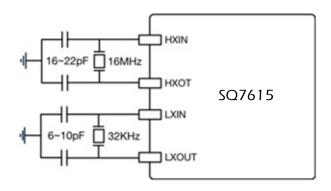

#### 2. External Crystal:

# External Crystal

FIGURE 2-5 SQ7615 RECOMMENDED EXTERNAL APPLICATION CIRCUITS (EXTERNAL CRYSTAL)

#### 3. Power Decoupling:

# Power Jack VDD 0.1uF

Power Decoupling Cap

**REG** SQ7615 **VSS**

FIGURE 2-6 SQ7615 RECOMMENDED EXTERNAL APPLICATION CIRCUITS (POWER DECOUPLING)

Note: The 0.1uF near the VDD should be as close as possible to the IC

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

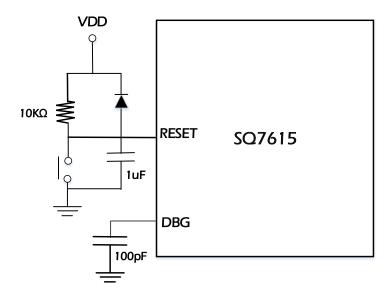

#### 4. RESET and DBG pin:

FIGURE 2-7 SQ7615 RECOMMENDED EXTERNAL APPLICATION CIRCUITS (RESET AND DBG PIN)

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

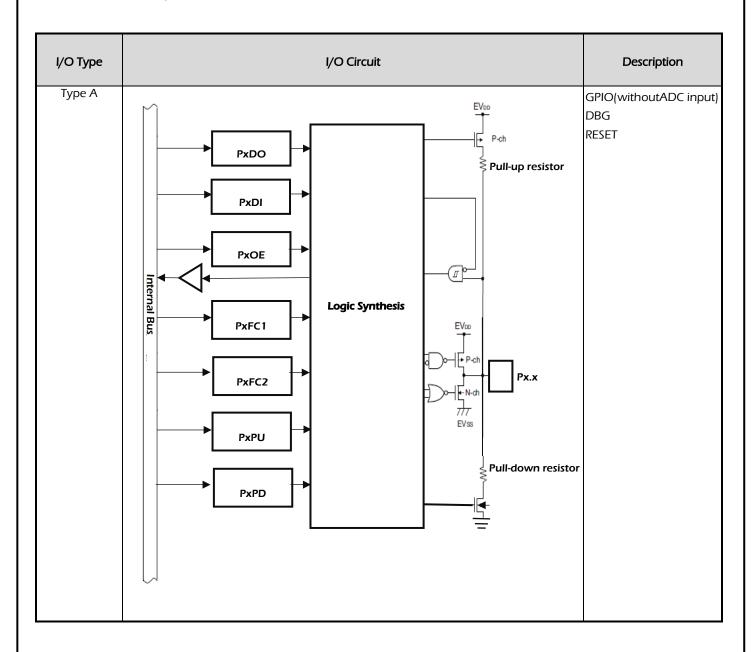

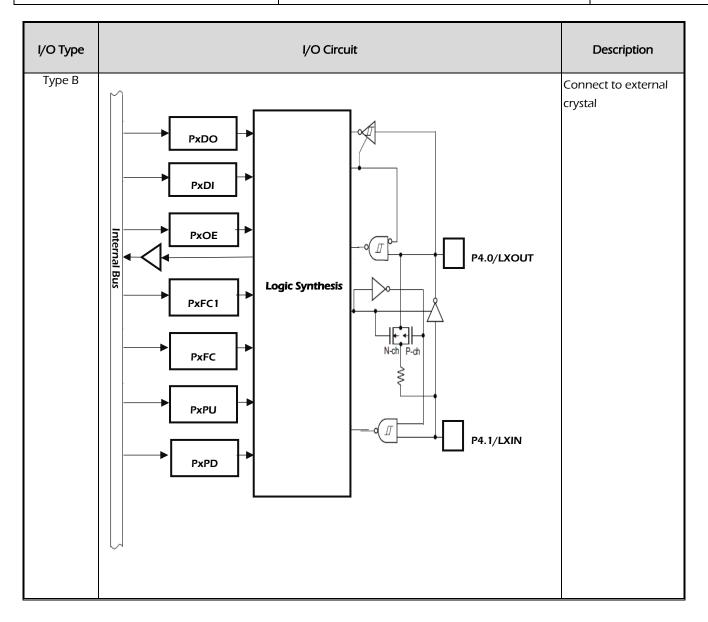

# 2.5 I/O Circuit type

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

Page: 24 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

# 3. Electronic Characteristics

# 3.1 Absolute Maximum Ratings

The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

$(V_{SS} = 0V)$

| Parameter              | Symbol           | Pins         | Ratings         | Unit |

|------------------------|------------------|--------------|-----------------|------|

| Supply Voltage         | $V_{DD}$         |              | -0.3 to 6.0     | V    |

| Input Voltage          | V <sub>IN</sub>  | All I/O pins | -0.3 to VDD+0.3 | V    |

| Output Current (total) |                  | All I/O pins | 100             | mA   |

| Storage Temperature    | T <sub>STG</sub> |              | -50 to 125      | °C   |

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

# 3.2 Operation Conditions

The following defines the electrical characteristics of the device when it is operated at voltage and temperature maximum/minimum values. Unless otherwise stated, the standard conditions were determined at "operating temperature 25  $^{\circ}$  C and operating voltage VDD = 3.3 V".

### 3.2.1 Operation Conditions

| Parameter             | Symbol    | Condition | Min  | Тур. | Max  | Unit |

|-----------------------|-----------|-----------|------|------|------|------|

| Supply Voltage        | $V_{DD}$  |           | 2.0  | 3.3  | 5.5  | V    |

| Analog Supply Voltage | $V_{DDA}$ |           | 2.0  | 3.3  | 5.5  | V    |

| Reset Voltage(Note)   | $V_{RST}$ |           | 1.89 | 1.95 | 2.01 | V    |

| Operating Temperature | Та        |           | -40  | 25   | 85   | °C   |

Note:  $V_{RST}$  as the BROR 1st level

#### 3.2.2 Clock Timing

| Parameter                        | Symbol             | Condition                                     | Min      | Тур.  | Max      | Unit    |

|----------------------------------|--------------------|-----------------------------------------------|----------|-------|----------|---------|

| External Clock Source            |                    |                                               |          |       |          |         |

| Low frequency external crystal   | f <sub>LXIN</sub>  |                                               |          | 32768 |          | Hz      |

| (note 1)                         |                    |                                               |          | 32768 |          | HZ      |

| High frequency external crystal  | f <sub>HXIN</sub>  |                                               |          |       | 1.6      |         |

| (note 1)                         |                    |                                               | 1        |       | 16       | MHz     |

| Internal Clock Source            |                    |                                               |          |       | l        |         |

| Low frequency internal reference | f                  | T <sub>A</sub> = 25°C                         | -25%     | 32    | + 25%    | kHz     |

| clock                            | $f_{LIRC}$         | 1A - 23 C                                     | -2370    | 32    | 1 2370   | KI IZ   |

|                                  |                    | $T_A = 25^{\circ}C$                           | - 1%     | 1     | + 1%     | NAL I-  |

| Low power internal reference     | _                  | $T_A = 0 \sim 50^{\circ}C \text{ (note 2)}$   | - 1%     | 1     | + 1%     |         |

| clock                            | f <sub>LPIRC</sub> | $T_A = -20 \sim 70^{\circ}C \text{ (note2)}$  | - 1.5%   | 1     | + 1.5%   | MHz     |

|                                  |                    | T <sub>A</sub> = -40~ 85°C                    | - 3%     | 1     | + 3%     |         |

|                                  |                    | T <sub>A</sub> = 25°C                         | - 1%     | 16    | + 1%     |         |

| High frequency internal          |                    | $T_A = 0 \sim 50^{\circ}C \text{ (note 2)}$   | - 1%     | 16    | + 1%     | N 41 1- |

| reference clock                  | f <sub>HIRC</sub>  | $T_A = -20 \sim 70^{\circ}C \text{ (note 2)}$ | - 1.5%   | 16    | + 1.5%   | MHz     |

|                                  |                    | T <sub>A</sub> = -40~ 85°C                    | - 3%     | 16    | + 3%     |         |

| Phase-locked loop                | f <sub>PLL</sub>   | T <sub>A</sub> = 25°C                         | (note 3) | 24    | (note 3) | MHz     |

Note 1: It takes around 2.5ms from high frequency external oscillation starts to fully oscillating (high frequency external oscillation is 16MHz, Topr=  $25^{\circ}$ C). It takes around 1.2 sec from low frequency external oscillation starts to fully oscillating (low frequency external oscillation is 32KHz, Topr= $25^{\circ}$ C).

Page: 26 / 352

iMQ reserves the right to change the information in this document without prior notice. Please contact iMQ to obtain the latest version of product specification before placing your order. Use of iMQ devices in life support is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless iMQ from any and all damages, claims, suits or expenses resulting from such use.

iMQ Technology Inc.

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

Note 2 : The test condition is VDD=  $5V \pm 10\%$

Note 3: The accuracy of  $f_{PLL}$  is  $\pm$ /- 1%, which is the same as PLL reference clock source (16MHz  $f_{HXIN}$  or  $f_{LPIRC}$ )

# 3.2.3 I/O Characteristics

| VDD=3.3V ,Ta=-40~85 |                     |               |          |      |          |      |

|---------------------|---------------------|---------------|----------|------|----------|------|

| Parameter           | Symbol              | Condition     | Min      | Тур. | Max      | Unit |

| Input low voltage   | V <sub>IL</sub>     |               | 0        |      | 0.25 VDD | V    |

| Input high voltage  | V <sub>IH</sub>     |               | 0.75 VDD |      | VDD      | V    |

| Output low voltage  | V <sub>OL_050</sub> | IOL=5 mA      |          |      | 0.4      | V    |

| Output high voltage | V <sub>OH_015</sub> | IOH=1.5 mA    | VDD-0.4  |      |          | V    |

| Output low current  |                     | SDR=0,0.1xVDD | 2.5      | 6.7  |          | mA   |

| Output low current  | l <sub>OL</sub>     | SDR=0,0.3xVDD | 7        | 15   |          | mA   |

| Output high surrout |                     | SDR=0,0.9xVDD | 1        | 2.4  | -        | mA   |

| Output high current | I <sub>OH</sub>     | SDR=0,0.7xVDD | 3        | 5.8  |          | mA   |

| Pull-up Resistance  | R <sub>PULLUP</sub> |               | 10       | 20   | 40       | kΩ   |

| Pull-low Resistance | R <sub>PULLDN</sub> |               | 10       | 20   | 40       | kΩ   |

| VDD=5V ,Ta=-40~85°  |                     |               |          |      |          | 10~85°C |

|---------------------|---------------------|---------------|----------|------|----------|---------|

| Parameter           | Symbol              | Condition     | Min      | Тур. | Max      | Unit    |

| Input low voltage   | V <sub>IL</sub>     |               | 0        |      | 0.25 VDD | V       |

| Input high voltage  | V <sub>IH</sub>     |               | 0.75 VDD |      | VDD      | V       |

| Output low voltage  | V <sub>OL_100</sub> | IOL=10 mA     |          |      | 0.6      | V       |

| Output high voltage | V <sub>OH_035</sub> | IOH= 3.5 mA   | VDD-0.6  |      |          | V       |

| Output law gurrant  |                     | SDR=0,0.1xVDD | 6        | 13.5 |          | mA      |

| Output low current  | l <sub>OL</sub>     | SDR=0,0.3xVDD | 15       | 31   |          | mA      |

| Output high surrout |                     | SDR=0,0.9xVDD | 2.5      | 4.8  | -        | mA      |

| Output high current | I <sub>OH</sub>     | SDR=0,0.7xVDD | 6.5      | 12   |          | mA      |

| Pull-up Resistance  | R <sub>PULLUP</sub> |               | 10       | 20   | 40       | kΩ      |

| Pull-low Resistance | R <sub>PULLDN</sub> |               | 10       | 20   | 40       | kΩ      |

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

# 3.3 D.C. Characteristics

|                                           |                     |                                                                               | Ор  | erating @ 3 | .3V, Ta=-40 | ~85°C |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------------|-----|-------------|-------------|-------|

| Parameter                                 | Symbol              | Condition                                                                     | Min | Тур.        | Max         | Unit  |

|                                           | I <sub>DD_N0</sub>  | LPIRC is PLL clock source<br>f <sub>LPIRC</sub> =1MHz,fsyscIk=24MHz<br>(PLL)  | -   | 5.5         | 8.5         | mA    |

| Normal Mode                               | I <sub>DD_N1</sub>  | System clock is HIRC<br>f <sub>HXIN</sub> =0MHz,fsysclk=16 MHz<br>(HIRC)      | -   | 2.7         | 4.2         | mA    |

| (LIRC on, code executing from flash)      | I <sub>DD_N2</sub>  | System clock is LIRC only LIRC enable, others are stopped., fsysclk=32KHz     | -   | 0.7         | 1.1         | mA    |

|                                           | I <sub>DD_N3</sub>  | System clock is HXTAL<br>fsysclk=16MHz<br>(HXTAL)                             | -   | 3.8         | 5.7         | mA    |

|                                           | I <sub>DD_N4</sub>  | System clock is LXTAL<br>fsysclk=32768Hz<br>(LXTAL)                           | -   | 0.7         | 1.1         | mA    |

|                                           | I <sub>DD_SL0</sub> | LPIRC is PLL clock source<br>f <sub>LPIRC</sub> =1MHz, fsyscIk=24MHz<br>(PLL) | -   | 2.7         | 4.1         | mA    |

| Sleep Mode                                | I <sub>DD_SL1</sub> | System clock is HIRC<br>f <sub>HXIN</sub> =0MHz,HIRC=16 MHz<br>(HIRC)         | -   | 1.3         | 2.1         | mA    |

| (LIRC on, CPU clock is stopped)           | I <sub>DD_SL2</sub> | System clock is LIRC<br>fsysclk=32KHz<br>(LIRC)                               | -   | 0.7         | 1.1         | mA    |

|                                           | I <sub>DD_SL3</sub> | System clock is HXTAL<br>fsysclk=16MHz<br>(HXTAL)                             | -   | 2.0         | 3.1         | mA    |

|                                           | I <sub>DD_SL4</sub> | System clock is LXTAL<br>fsysclk=32768Hz<br>(LXTAL)                           | -   | 0.7         | 1.1         | mA    |

| Deep Sleep Mode (LIRC on, CPU and RAM are | I <sub>DD_DS0</sub> | RTC Disable                                                                   | -   | 1.0         | -           | uA    |

| retained.)                                | I <sub>DD_DS1</sub> | RTC Enable, LXTAL on                                                          | -   | 1.6         | -           | uA    |

| Operating @ 3.3V, Ta=2               |                     |                      |     |      |     |      |

|--------------------------------------|---------------------|----------------------|-----|------|-----|------|

| Parameter Symb                       |                     | Condition            | Min | Тур. | Max | Unit |

| Deep Sleep Mode                      | I <sub>DD_DS0</sub> | RTC Disable          | 0.8 | 1.0  | -   | uA   |

| (LIRC on, CPU and RAM are retained.) | I <sub>DD_DS1</sub> | RTC Enable, LXTAL on | 1.4 | 1.6  | -   | uA   |

iMQ Technology Inc.

Name: SQ7615 Datasheet Version: V1.3 No.: TDDS01-S7615-EN

|                                           |                            |                                                                               |     | Operating @ | 9 5V,Ta=-40 | )~85°C |

|-------------------------------------------|----------------------------|-------------------------------------------------------------------------------|-----|-------------|-------------|--------|

| Parameter                                 | Parameter Symbol Condition |                                                                               | Min | Тур.        | Max         | Unit   |

|                                           | I <sub>DD_N0</sub>         | LPIRC is PLL clock source<br>f <sub>LPIRC</sub> =1MHz,fsyscIk=24MHz<br>(PLL)  | -   | 5.5         | 8.5         | mA     |

| Normal Mode                               | I <sub>DD_N1</sub>         | System clock is HIRC<br>f <sub>HXIN</sub> =0MHz,fsyscIk=16 MHz<br>(HIRC)      | -   | 2.7         | 4.2         | mA     |

| (LIRC on, code executing from flash)      | I <sub>DD_N2</sub>         | System clock is LIRC only LIRC enable, others are stopped., fsysclk=32KHz     | -   | 0.8         | 1.2         | mA     |

|                                           | I <sub>DD_N3</sub>         | System clock is HXTAL<br>fsysclk=16MHz<br>(HXTAL)                             | -   | 3.8         | 5.7         | mA     |

|                                           | I <sub>DD_N4</sub>         | System clock is LXTAL<br>fsysclk=32768Hz<br>(LXTAL)                           | -   | 0.8         | 1.2         | mA     |

|                                           | I <sub>DD_SL0</sub>        | LPIRC is PLL clock source<br>f <sub>LPIRC</sub> =1MHz, fsysclk=24MHz<br>(PLL) | -   | 2.7         | 4.1         | mA     |

| Sleep Mode                                | I <sub>DD_SL1</sub>        | System clock is HIRC<br>f <sub>HXIN</sub> =0MHz,HIRC=16 MHz<br>(HIRC)         | -   | 1.3         | 2.1         | mA     |

| (LIRC on, CPU clock is stopped)           | I <sub>DD_SL2</sub>        | System clock is LIRC<br>fsyscIk=32KHz<br>(LIRC)                               | -   | 0.8         | 1.2         | mA     |

|                                           | I <sub>DD_SL3</sub>        | System clock is HXTAL<br>fsysclk=16MHz<br>(HXTAL)                             | -   | 2.0         | 3.1         | mA     |

|                                           | I <sub>DD_SL4</sub>        | System clock is LXTAL<br>fsysclk=32768Hz<br>(LXTAL)                           | -   | 0.8         | 1.2         | mA     |

| Deep Sleep Mode (LIRC on, CPU and RAM are | I <sub>DD_DS0</sub>        | RTC Disable                                                                   | -   | 1.1         | -           | uA     |

| retained.)                                | I <sub>DD_DS1</sub>        | RTC Enable, LXTAL on                                                          | -   | 1.8         | -           | uA     |

| Operating @ 5V,Ta=25°                |                     |                      |     |      |     |      |

|--------------------------------------|---------------------|----------------------|-----|------|-----|------|

| Parameter                            | Symbol              | Condition            | Min | Тур. | Max | Unit |

| Deep Sleep Mode                      | I <sub>DD_DS0</sub> | RTC Disable          | 0.9 | 1.1  | -   | uA   |

| (LIRC on, CPU and RAM are retained.) | I <sub>DD_DS1</sub> | RTC Enable, LXTAL on | 1.5 | 1.8  | -   | uA   |

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

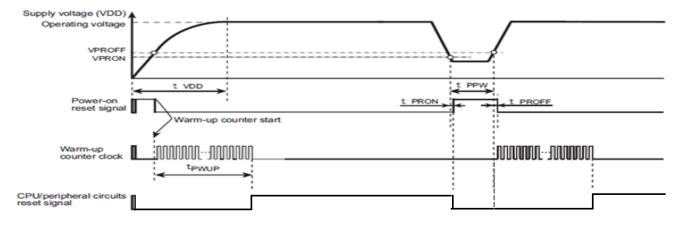

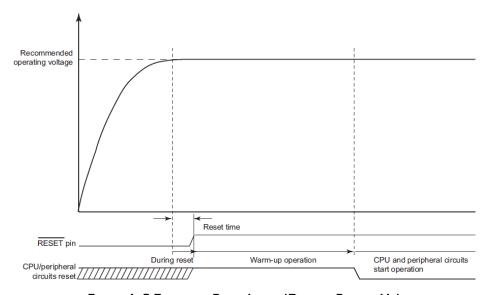

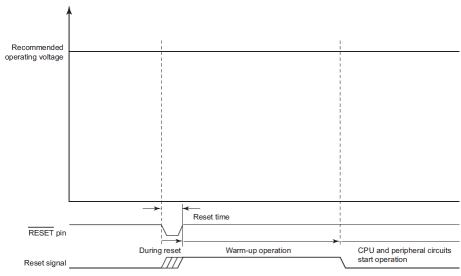

#### 3.4 **Power-on Reset Characteristics**

|        |                                                            |      |      | Vss=0,Ta= | -40~85°C |

|--------|------------------------------------------------------------|------|------|-----------|----------|

| Symbol | Condition                                                  | Min  | Тур. | Max       | Unit     |

| VPROFF | Power-on reset releasing voltage                           | 1.89 | 1.95 | 2.01      | V        |

| VPRON  | Power-on reset detecting voltage                           | 1.84 | 1.90 | 1.96      | V        |

| tPROFF | Power-on reset releasing response time                     | -    | 0.01 | 0.1       | ms       |

| tPRON  | Power-on reset detecting response time                     | -    | 0.01 | 0.1       | ms       |

| tPPW   | Power-on reset minimum pulse width                         | 1    | -    | 1         | ms       |

| tPWUP  | Warming-up time after a reset is clear and CPU ready(Note) | -    | 4    | -         | ms       |

| tVDD   | Power supply rise time                                     | 0.5  | -    | 5         | ms       |

Note: tPWUP does not include BOOTROM code execution time. BOOTROM code execution time is around 50ms.

FIGURE 3-1 OPERATION TIMING OF POWER ON RESET

No.: TDDS01-S7615-EN Name: SQ7615 Datasheet Version: V1.3

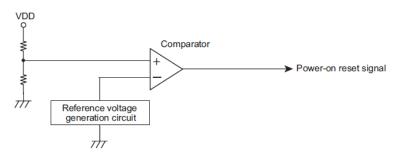

#### 3.5 **BROR Characteristics**

|           |           |                                   |      |      | Ta=-4 | 0~85°C |

|-----------|-----------|-----------------------------------|------|------|-------|--------|

| Parameter | Symbol    | Condition                         | Min  | Тур. | Max   | Unit   |

|           | VBRORON1  | 1st level DDODCEC-00              | 1.84 | 1.90 | 1.96  | V      |

|           | VBROROFF1 | 1 <sup>st</sup> level,BRORCFG=00  | 1.89 | 1.95 | 2.01  | V      |

|           | VBRORON2  | and I I DODGEG 01                 | 2.18 | 2.25 | 2.32  | V      |

| BROR      | VBROROFF2 | 2 <sup>nd</sup> level,BRORCFG=01  | 2.23 | 2.30 | 2.37  | V      |

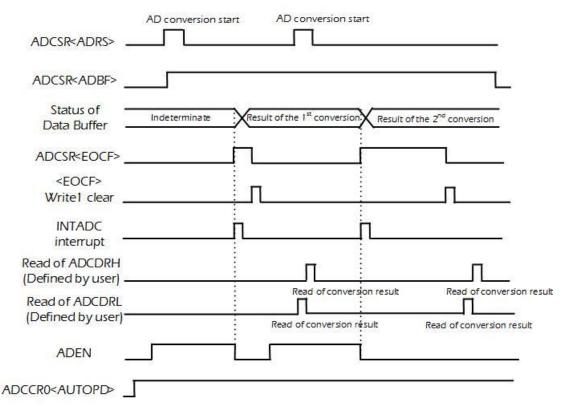

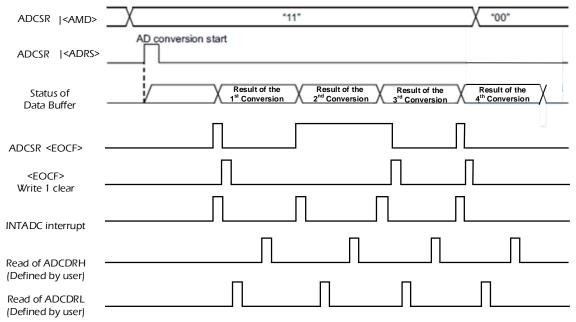

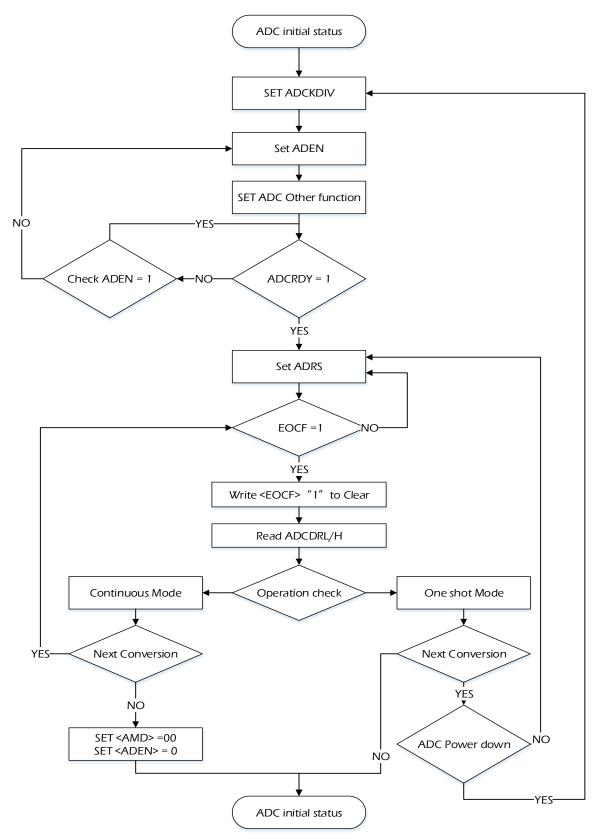

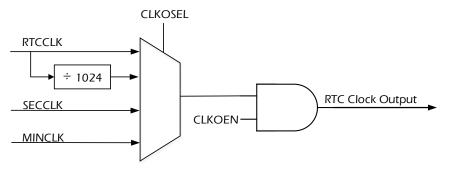

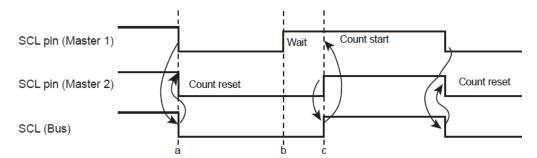

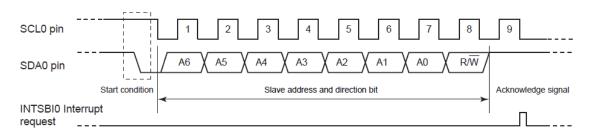

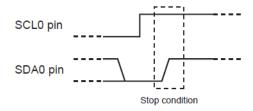

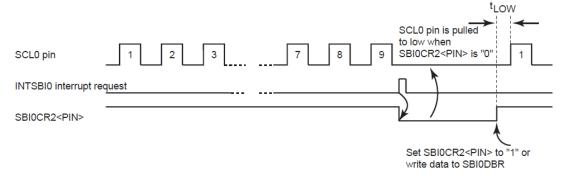

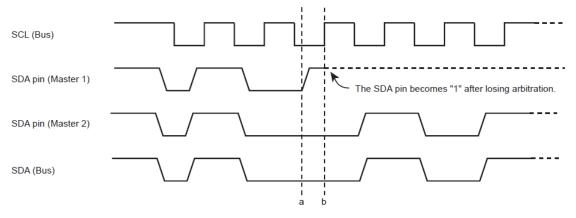

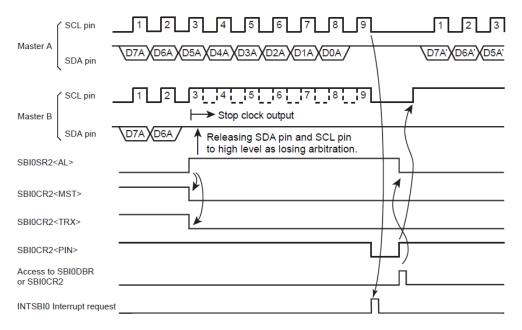

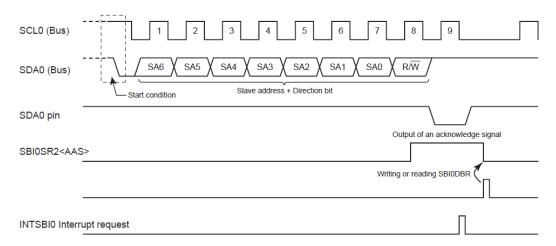

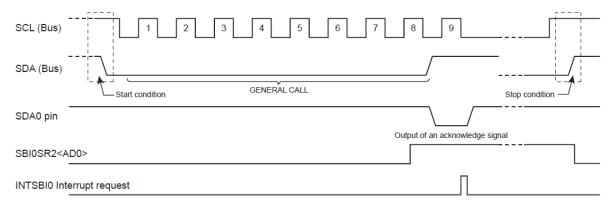

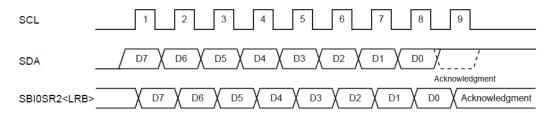

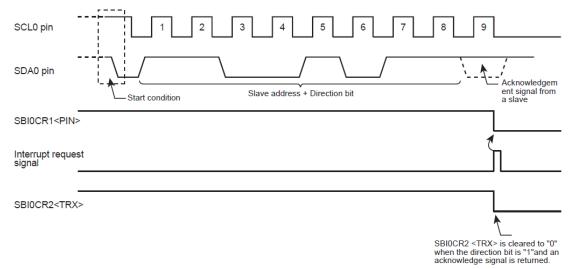

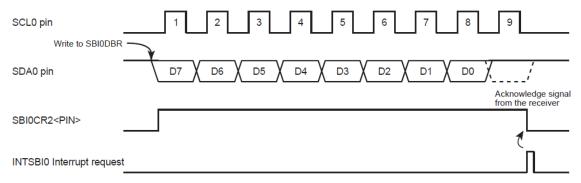

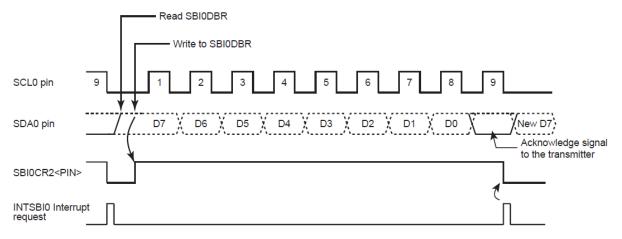

| BKOK      | VBRORON3  | 3 <sup>rd</sup> level,BRORCFG=10  | 2.47 | 2.55 | 2.63  | V      |